OKI ARM-BASED MICROCONTROLLER PRODUCTS

# ML674001/ML675001 Series

January 31, 2004

# Preface

This Development Specification contains hardware and software specifications of Oki Electric's ML674001 Series/ML675001 Series 32-bit microcontroller. The manuals shown below are also available, and should be consulted a necessary.

#### **ARM Architecture Reference Manual**

• Description of ARM instruction set architecture

#### **ARM7TDMI Data Sheet**

- Description of ARM7TDMI instruction set

- Description of ARM7TDMI operation

The above documents are published by ARM Corporation. Please ensure that you refer to the latest versions.

# Notation

This manual uses the following notational conventions.

| Туре       | Notation    | Meaning                                                                                                       |

|------------|-------------|---------------------------------------------------------------------------------------------------------------|

| ■ Numerals | 0xnn        | Hexadecimal number                                                                                            |

| ■ Address  | 0xnnnn_nnnn | Hexadecimal number (It's means '0xnnnnnn')                                                                    |

| Units      | word, WORD  | 1  word = 32  bits                                                                                            |

|            | byte, BYTE  | 1 byte = 8 bits                                                                                               |

|            | M (mega-)   | $10^{6}$                                                                                                      |

|            | K (Kilo-)   | $2^{10} = 1024$                                                                                               |

|            | k (kilo-)   | $10^3 = 1000$                                                                                                 |

|            | m (milli-)  | $10^{-3}$                                                                                                     |

|            | μ (micro)   | $10^{-6}$                                                                                                     |

|            | n (nano-)   | 10 <sup>-9</sup>                                                                                              |

|            | S           | second(s)                                                                                                     |

| Terms      | "H" level   | The VIH or VOH voltage level stipulated in the Electrical<br>Characteristics as the voltage high signal level |

|            | "L" level   | The VIL or VOL voltage level stipulated in the Electrical<br>Characteristics as the voltage low signal level  |

# Table of Contents

# Chapter 1 Introduction

| 1.1 Features                        |  |

|-------------------------------------|--|

| 1.2 Functional Blocks               |  |

| 1.2.1 ML674001 series Block Diagram |  |

| 1.2.2 ML675001 series Block Diagram |  |

| 1.3 Pins                            |  |

| 1.3.1 Pin Layout                    |  |

| 1.3.1.1 LFBGA                       |  |

| 1.3.1.2 LQFP                        |  |

| 1.3.2 Pin List                      |  |

| 1.3.3 Pin Descriptions              |  |

| 1.3.4 Pin States                    |  |

| 1.3.5 Pin Structure and Treatment   |  |

| 1.3.6 Treatment of Unused Pins      |  |

|                                     |  |

# Chapter 2 CPU

| 2.1 Overview                                              |  |

|-----------------------------------------------------------|--|

| 2.2 CPU Operation States                                  |  |

| 2.2.1 State Transitions                                   |  |

| 2.3 Address Space                                         |  |

| 2.4 Memory Format                                         |  |

| 2.5 Instruction Length                                    |  |

| 2.6 Data Types                                            |  |

| 2.7 Processor Modes                                       |  |

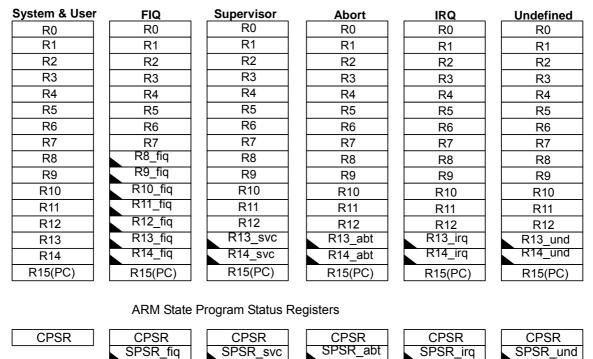

| 2.8 Registers                                             |  |

| 2.8.1 ARM State Registers                                 |  |

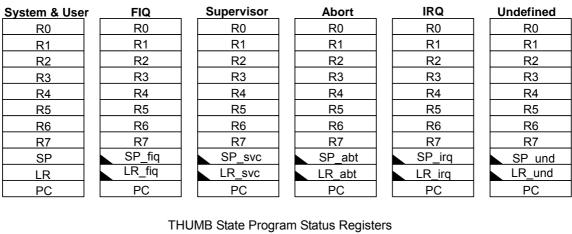

| 2.8.2 THUMB State Registers                               |  |

| 2.8.3 Relationships Between ARM and THUMB State Registers |  |

| 2.8.4 Accessing Upper Registers from THUMB State          |  |

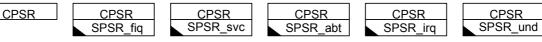

| 2.9 Program Status Registers                              |  |

| 2.9.1 Condition Code Flags                                |  |

| 2.9.2 Control Bits                                        |  |

| 2.9.3 Reserved Bits                                       |  |

| 2.10 Instruction Set Features                             |  |

| 2.10.1 ARM Instruction Set                                |  |

| 2.10.2 THUMB Instruction Set                              |  |

| 2.11 Addressing Modes                                     |  |

| 2.11.1 Load/Store Instructions                            |  |

| 2.11.2 Multiple Load/Store Instructions                   |  |

| 2.12 Exceptions                                           |  |

| 2.12.1 Switching to Exception Handler                     |  |

| 2.12.2 Returning from Exception Handler                   |  |

| 2.12.3 Summary of Exception Switching                     |  |

| 2.12.4 FIQ                                                |  |

| 2.12.5 IRQ                                                |  |

| 2.12.6 Aborts                                             |  |

| 2.12.7 Software Interrupts                                |  |

| 2.12.8 Undefined Instructions                             |  |

| 2.12.9 Exception Vectors                                  |  |

| 2.12.10 Exception Priority Order                          |  |

| 2.13 Resets                                               |  |

# Chapter 3 Address Mapping

| 3.1 Ov  | erview                          |  |

|---------|---------------------------------|--|

| 3.1.1   | Pin List                        |  |

| 3.1.2   | Register List                   |  |

| 3.2 Ad  | dress Map                       |  |

| 3.2.1   | ML674001 series address map     |  |

| 3.2.2   | ML675001 series address map     |  |

| 3.3 Reg | gister Descriptions             |  |

| 3.3.1   | Remap Control Register (RMPCON) |  |

| 3.3.2   | ROM Select Register (ROMSEL)    |  |

| 3.4 Rei | map Description                 |  |

| 3.4.1   | Remap Setting                   |  |

| 3.4.2   | Boot Control                    |  |

| 3.4.3   | Notes of Address map            |  |

| 3.4.4   | Remap Setting Example           |  |

## Chapter 4 Chip Configuration

| 4.1 Overview        |  |

|---------------------|--|

| 4.1.1 Pin List      |  |

| 4.2 Pin Description |  |

# Chapter 5 Clock Generator

| 5.1 Ove | rview                                               | 5-1 |

|---------|-----------------------------------------------------|-----|

| 5.1.1   | Components                                          | 5-1 |

| 5.1.2   | Pin List                                            | 5-2 |

| 5.1.3   | PLL Clock frequency setup (ML675001 Series Only. *) | 5-2 |

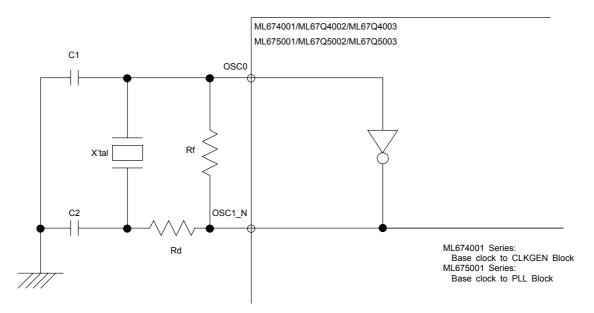

| 5.2 Sam | ple Crystal Connections                             | 5-2 |

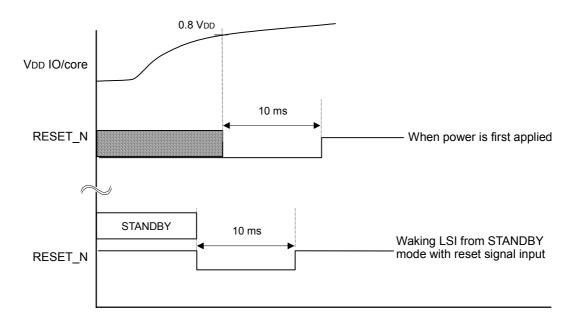

# Chapter 6 Reset Control

| 6.1 Overview                  | 6-1 |

|-------------------------------|-----|

| 6.1.1 Pin List                |     |

| 6.2 Reset Types               | 6-1 |

| 6.2.1 External Reset Input    |     |

| 6.2.2 Watchdog Timer Overflow |     |

| 6.3 Operational Description   |     |

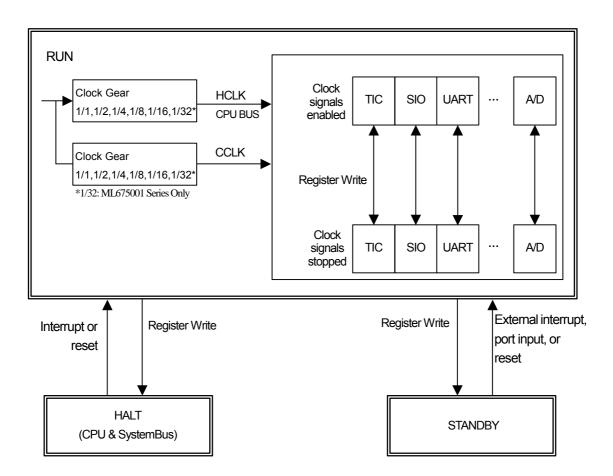

## Chapter 7 Power Management

| 7.1 Ove | erview                                      | 7-1  |

|---------|---------------------------------------------|------|

| 7.2 Pov | wer Management Functions                    |      |

| 7.2.1   | Register List                               |      |

| 7.3 Reg | gister Descriptions                         | 7-4  |

| 7.3.1   | Block Clock Control Register (BCKCTL)       | 7-4  |

| 7.3.2   | Clock Stop Register (CLKSTP)                |      |

| 7.3.3   | Clock Gear Control Register (CGBCNT0)       |      |

| 7.3.4   | Clock Wait Register (CKWT)                  |      |

| 7.3.5   | Stopping Clock Signals to Functional Blocks | 7-11 |

| 7.3.6   | Clock Gear                                  | 7-11 |

| 7.3.7   | HALT Mode                                   |      |

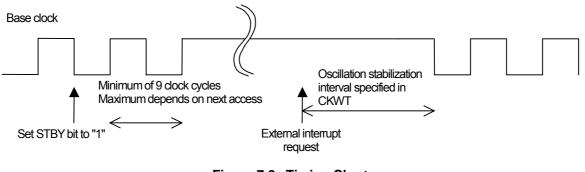

| 7.3.8   | STANDBY Mode                                |      |

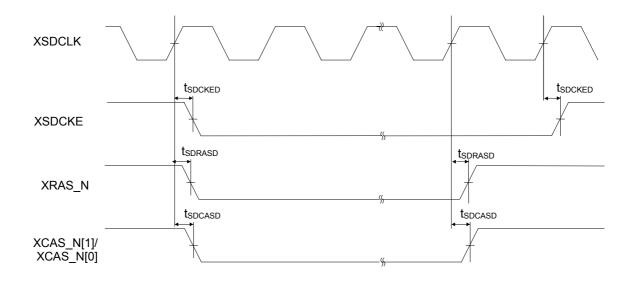

| 7.4 Usi | ing Power Management with DRAM              |      |

| 7.4.1   | Activating Self Refresh Operation           |      |

| 7.4.2   | Deactivating Self Refresh Operation         |      |

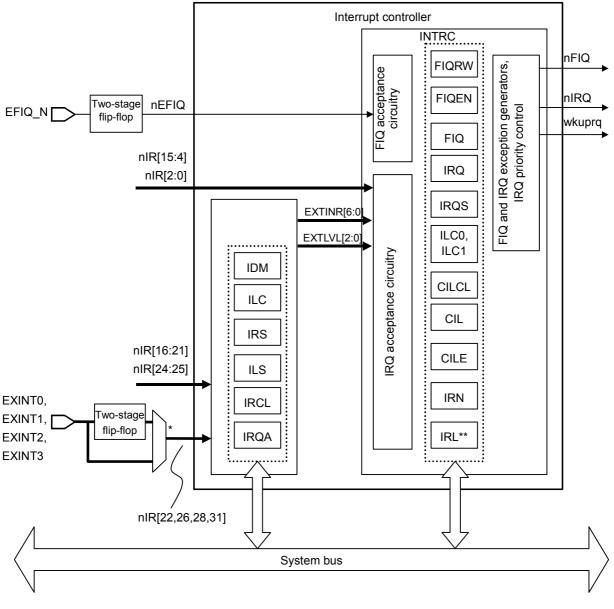

# Chapter 8 Interrupt Controller

| 8.1 | Overview                                                        |      |

|-----|-----------------------------------------------------------------|------|

| 8.1 | 1.1 Components                                                  |      |

| 8.1 | 1.2 Pin List                                                    |      |

| 8.1 | 1.3 Register List                                               |      |

| 8.2 | Interrupt Sources                                               |      |

| 8.2 | 2.1 External Fast Interrupt (EFIQ_N)                            |      |

| 8.2 | 2.2 External Interrupts (EXINT[n])                              |      |

| 8.2 | 2.3 Internal Interrupts (IRQn)                                  |      |

| 8.2 | 2.4 Interrupt Source List                                       |      |

| 8.3 | Interrupt Levels                                                |      |

| 8.4 | Register Descriptions                                           |      |

| 8.4 | 4.1 IRQ Register (IRQ)                                          |      |

| 8.4 | 4.2 Software Interrupt Register (IRQS)                          |      |

| 8.4 |                                                                 |      |

| 8.4 | 4.4 FIQRAW Register (FIQRAW)                                    |      |

| 8.4 | 4.5 FIQ Enable Register (FIQEN)                                 |      |

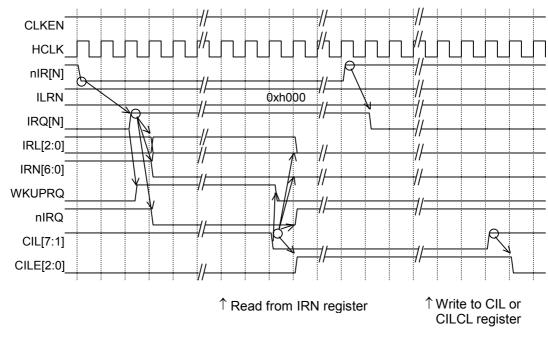

| 8.4 | 4.6 IRQ Number Register (IRN)                                   |      |

| 8.4 | 4.7 Current Interrupt Level Register (CIL)                      | 8-13 |

| 8.4 | 4.8 Interrupt Level Control Register 0 (ILC0)                   |      |

| 8.4 | 1.9 Interrupt Level Control Register 1 (ILC1)                   | 8-16 |

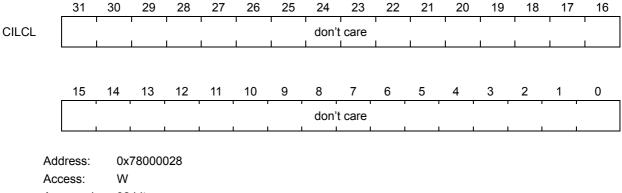

| 8.4 | 4.10 Current Interrupt Level Clear Register (CILCL)             |      |

| 8.4 | 4.11 Current Interrupt Level Encode Register (CILE)             |      |

| 8.4 | 4.12 IRQ Clear Register (IRCL)                                  |      |

| 8.4 | 4.13 IRQA Register (IRQA)                                       |      |

| 8.4 | IRQ Detection Mode Setting Register (IDM)                       |      |

| 8.4 | 4.15 Interrupt Level Control Register (ILC)                     |      |

|     | 1.16 Register Settings for Interrupt Sources                    |      |

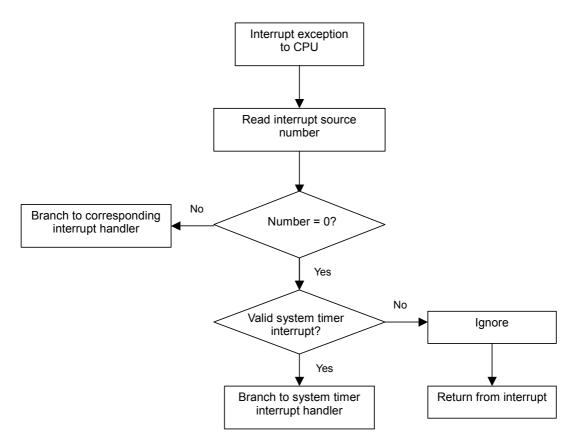

| 8.5 | Description of Operation                                        |      |

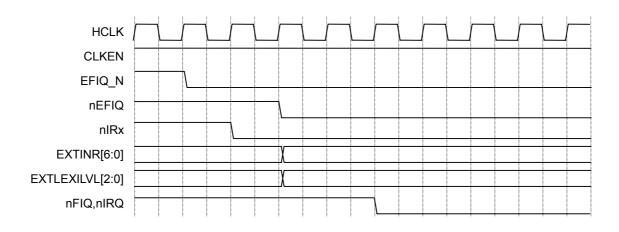

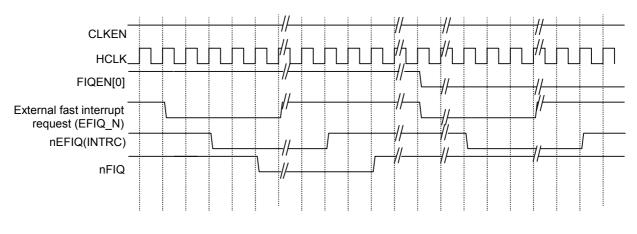

| 8.5 | 5.1 External Fast Interrupt (EFIQ_N)                            |      |

| 8.5 |                                                                 |      |

| 8.5 | 5.3 Nested Interrupts and Re-Entrant Interrupt Service Routines |      |

| 8.5 | 5.4 Important Notes on Interrupts                               |      |

| 8.5 | 5.5 Waking from HALT and STANDBY Modes                          |      |

| 8.5 | 5.6 Error Response                                              |      |

| 8.5 | 5.7 Interrupt Response Times                                    |      |

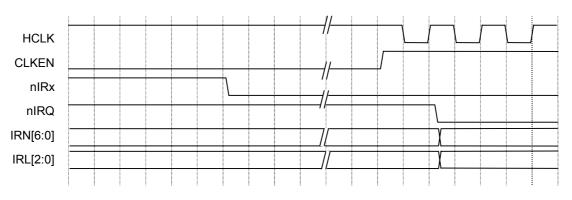

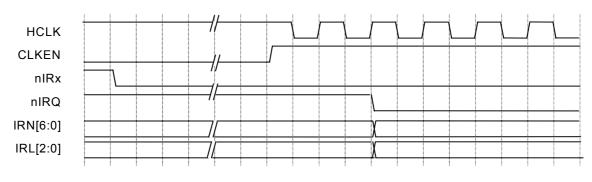

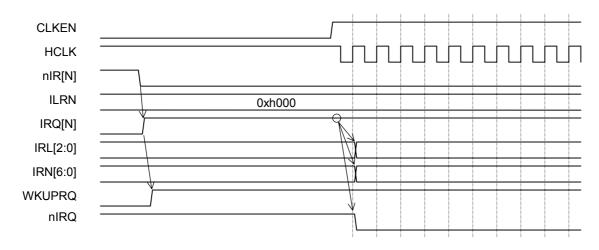

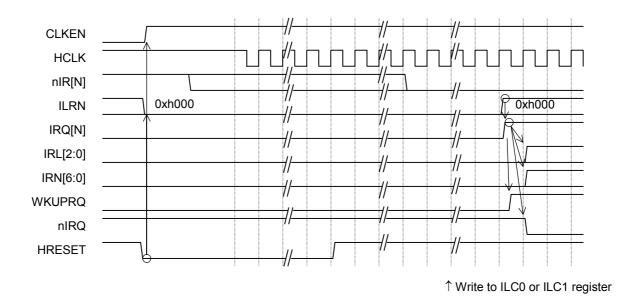

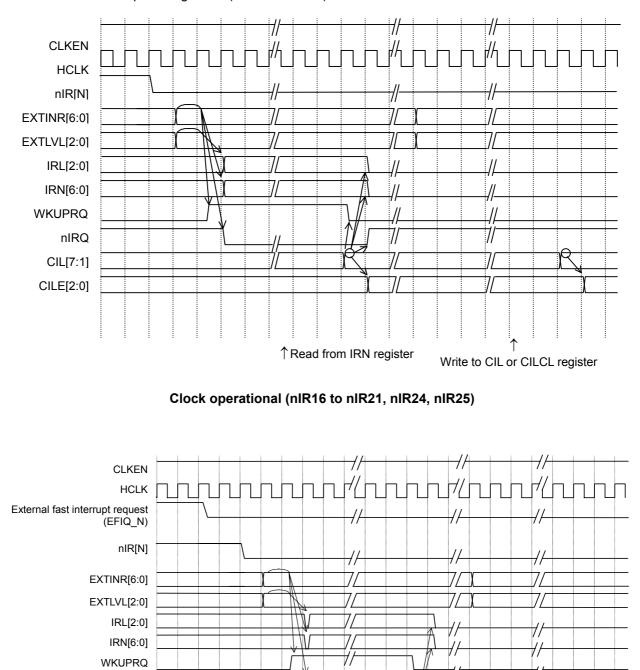

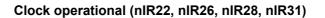

| 8.6 | Interrupt Acceptance Timing Charts                              |      |

| 8.6 | 5.1 FIQ Interrupt Timing Chart                                  |      |

| 8.6 |                                                                 |      |

| 8.6 | 5.3 IRQ Interrupt Timing Chart (nIR16 to nIR31)                 |      |

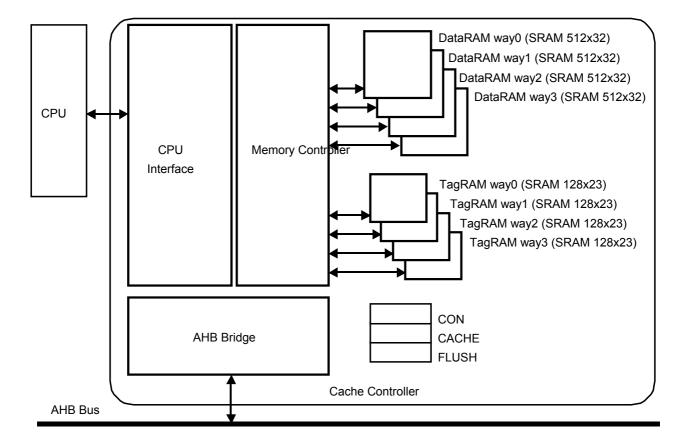

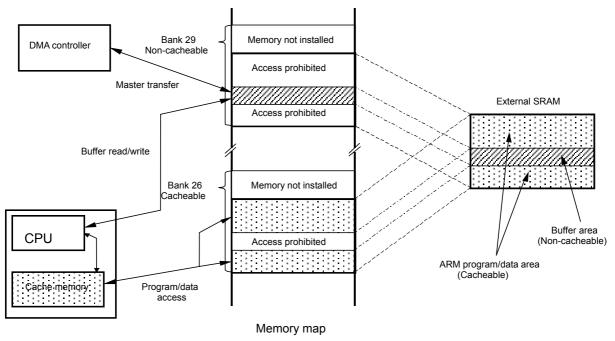

# Chapter 9 Cache Memory

| 9.1 Ov | erview                            |  |

|--------|-----------------------------------|--|

| 9.1.1  | Configuration                     |  |

|        | List of Control Registers         |  |

| 9.2 De | scription of Control Registers    |  |

|        | Cache Lock Control Register (CON) |  |

| 9.2.2  | Cacheable Register (CACHE)        |  |

|        | FLUSH Register (FLUSH)            |  |

|        | scription of Operations           |  |

|        | Initialization of Cache Memory    |  |

| 9.3.2  | Cacheable/Non-cacheable Setting   |  |

| 9.3.3  | Description of operations         |  |

|        |                                   |  |

| 9.3.4  | Lock Function                                              |  |

|--------|------------------------------------------------------------|--|

| 9.3.5  | Load Mode                                                  |  |

| 9.3.6  | Flushing Function                                          |  |

| 9.4 Pr | ecautions in Use                                           |  |

| 9.4.1  | Precautions when Using DMA Transfer                        |  |

| 9.4.2  | Precautions in Remapping                                   |  |

| 9.5 Ex | amples of Setting                                          |  |

| 9.5.1  | Example of Cache Memory Initialization                     |  |

| 9.5.2  | Example of Cache Memory Flushing Requiring Data Write Back |  |

| 9.5.3  | Example of Lock Setting Procedure                          |  |

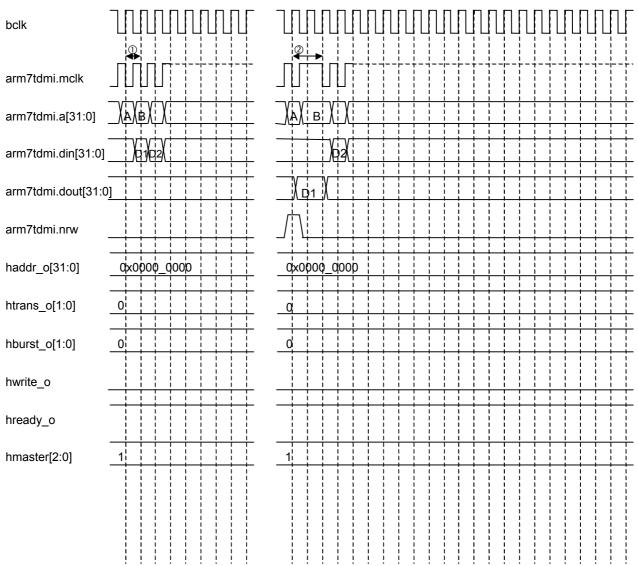

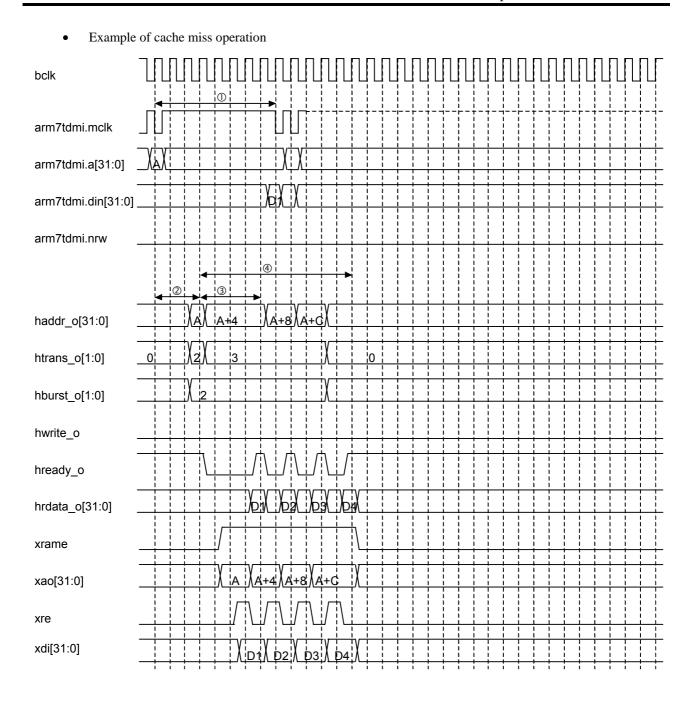

| 9.6 Ty | pical Operation Timings                                    |  |

## Chapter 10 Built-In Memory

| 10.1 | Overview               | 1 |

|------|------------------------|---|

| 10.2 | Built-In SRAM          | 1 |

| 10.3 | Built-In FLASH ROM 10- | 1 |

# Chapter 11 External Memory Controller

| 11.1 Ov | erview                                                                                | 11-1  |

|---------|---------------------------------------------------------------------------------------|-------|

| 11.1.1  | Pin List                                                                              | 11-1  |

| 11.1.2  | Register List                                                                         | 11-2  |

| 11.2 Re | gister Descriptions                                                                   | 11-3  |

|         | $\partial$                                                                            |       |

| 11.2.2  | External I/O bank 2/3 Bus Width Control Register (IO23BWC) (*1: ML675001 Series only) | 11-5  |

| 11.2.3  | External ROM Access Control Register (ROMAC)                                          | 11-6  |

| 11.2.4  | External SRAM Access Control Register (RAMAC)                                         | 11-8  |

|         | External I/O Bank 0/1 Access Control Register (IO01AC)                                |       |

| 11.2.6  | External I/O Bank 2/3 Access Control Register (IO23ACX *1, IO23ACY *2)                | 11-12 |

| 11.2.7  | DRAM Bus Width Control Register (DBWC)                                                | 11-14 |

|         | DRAM Control Register (DRMC)                                                          |       |

| 11.2.9  | DRAM Characteristics Control Register (DRPC)                                          | 11-17 |

|         | SDRAM Mode Register (SDMD)                                                            |       |

|         | DRAM Command Register (DCMD)                                                          |       |

| 11.2.12 | DRAM Refresh Cycle Control Register 0 (RFSH0)                                         | 11-21 |

| 11.2.13 | DRAM Refresh Cycle Control Register 1 (RFSH1)                                         | 11-22 |

|         | DRAM Power Down Control Register (RDWC)                                               |       |

| 11.3 Op | erational Description                                                                 | 11-25 |

|         | Bus Width                                                                             |       |

|         | ROM/SRAM Control                                                                      |       |

|         | I/O Banks Control                                                                     |       |

|         | DRAM Control                                                                          |       |

|         | Access Timing Parameters for DRAM                                                     |       |

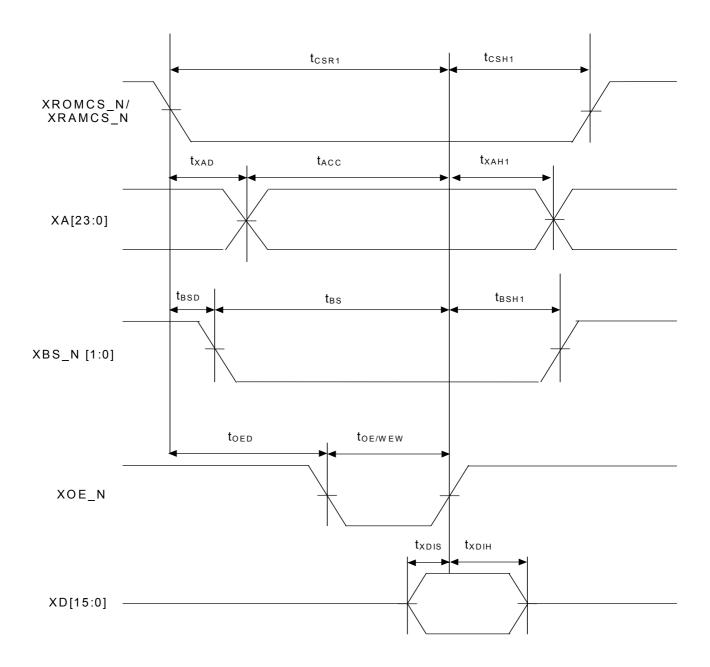

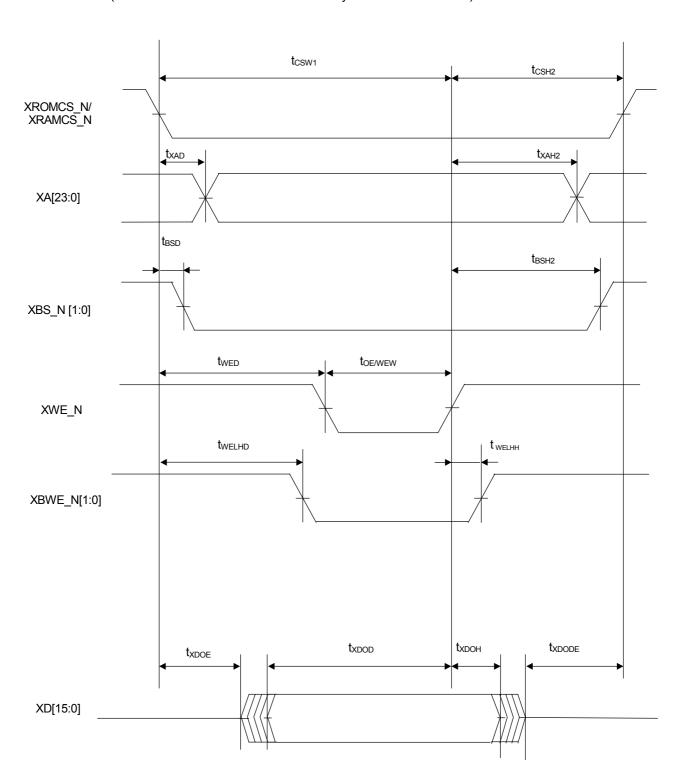

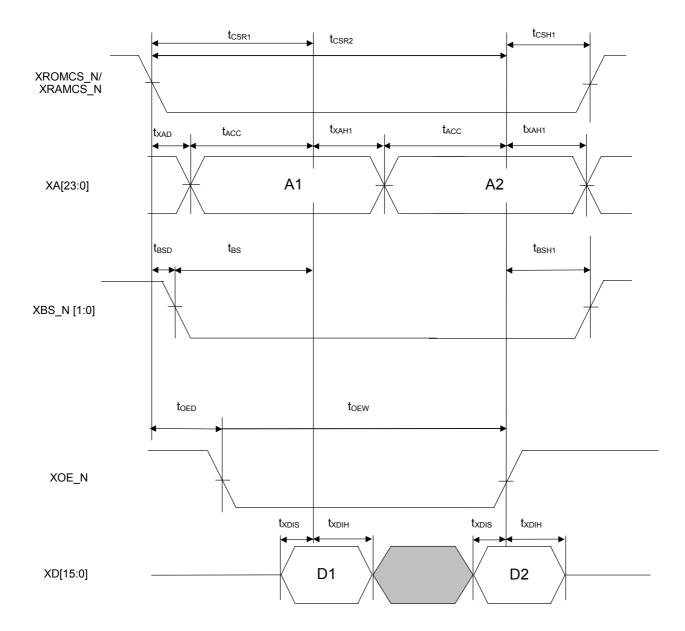

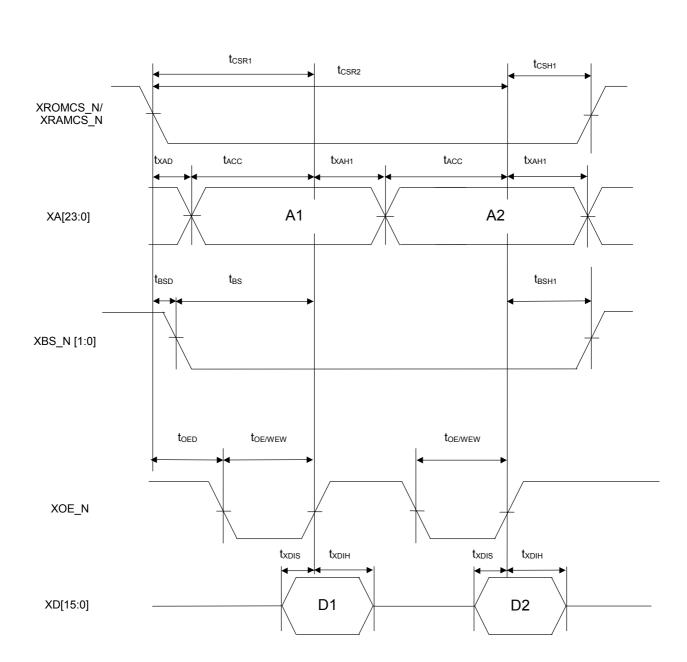

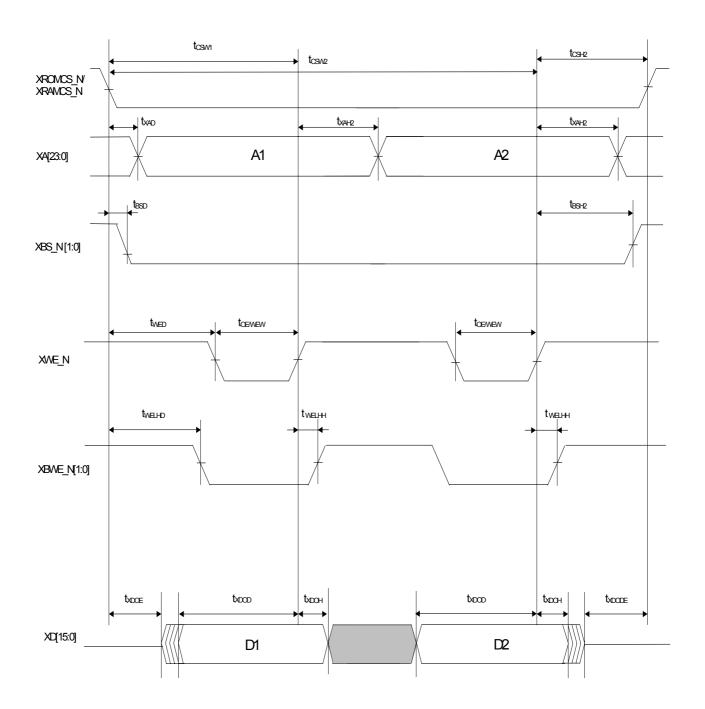

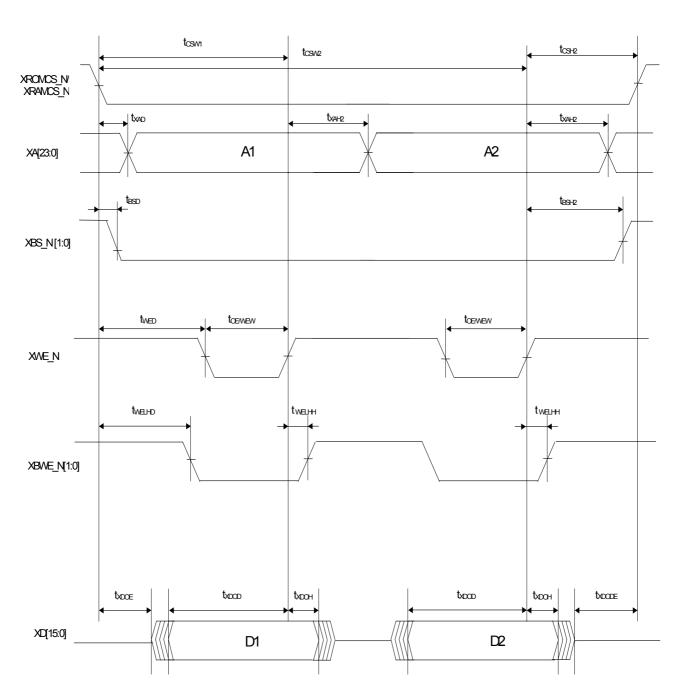

| 11.4 Ac | cess Timing                                                                           | 11-34 |

|         | Accessing External Devices                                                            |       |

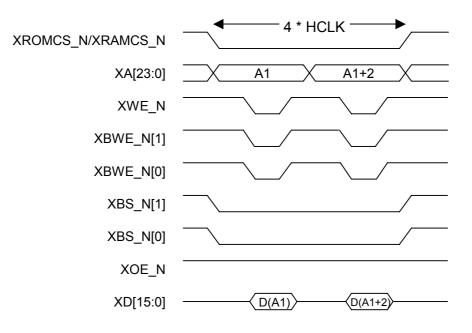

|         | .1 External ROM/RAM Access                                                            |       |

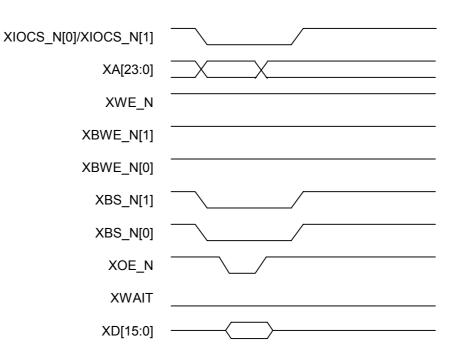

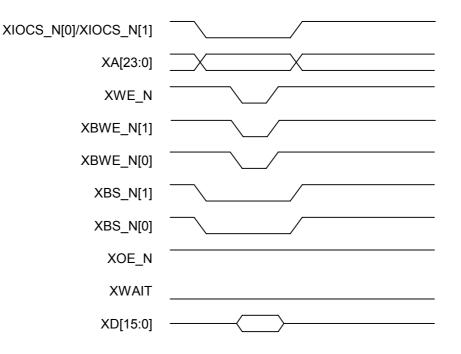

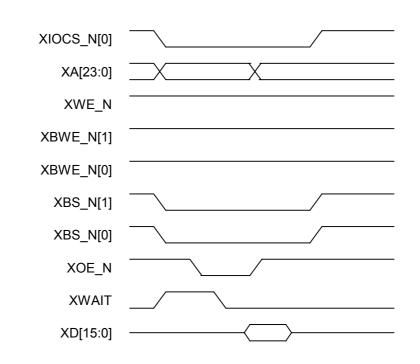

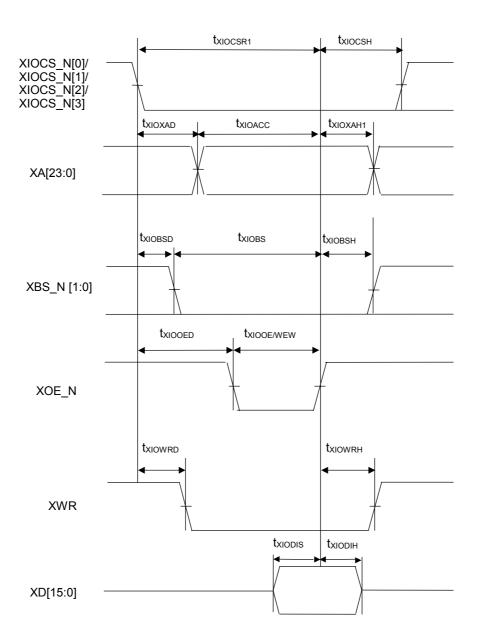

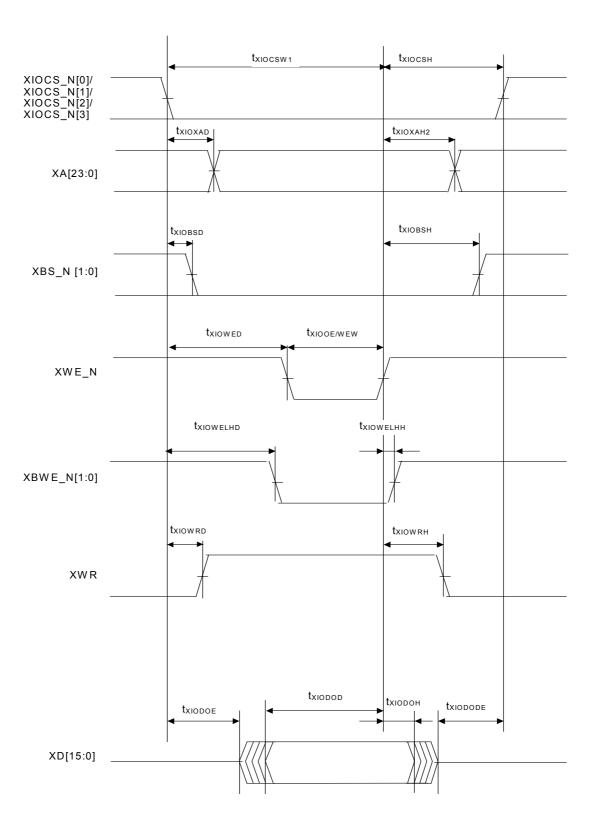

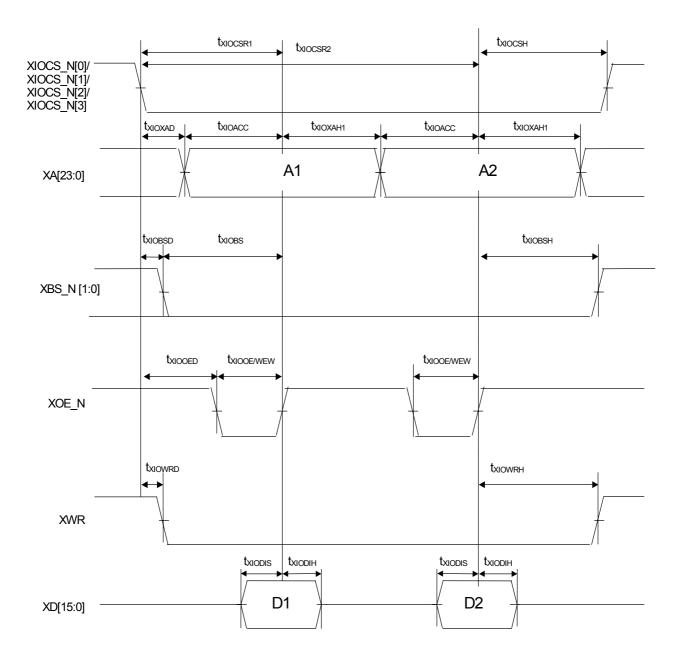

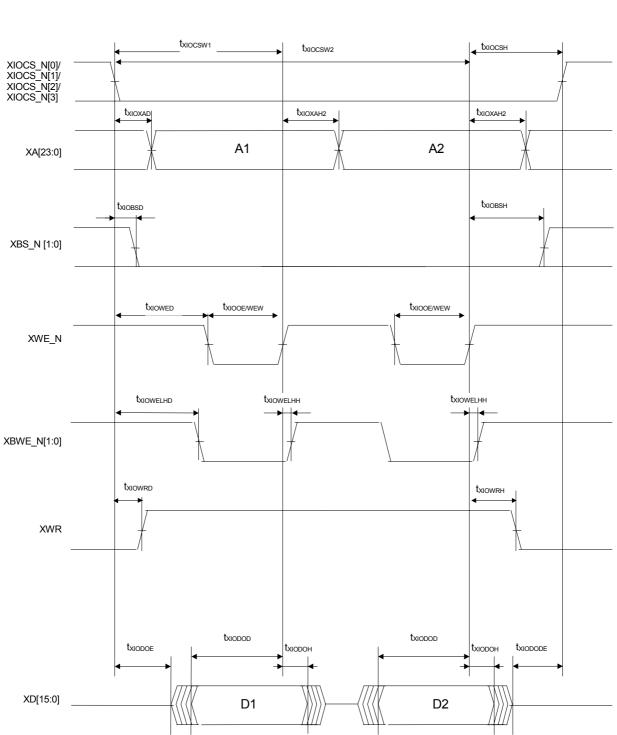

|         | .2 External I/O Bank Access                                                           |       |

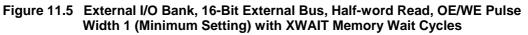

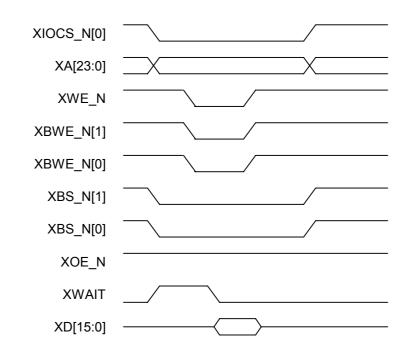

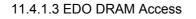

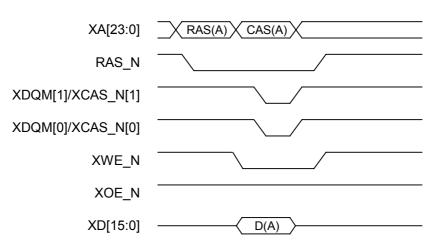

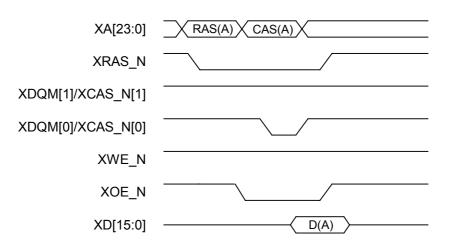

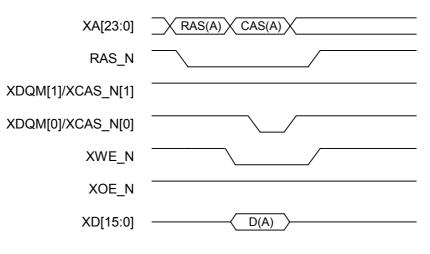

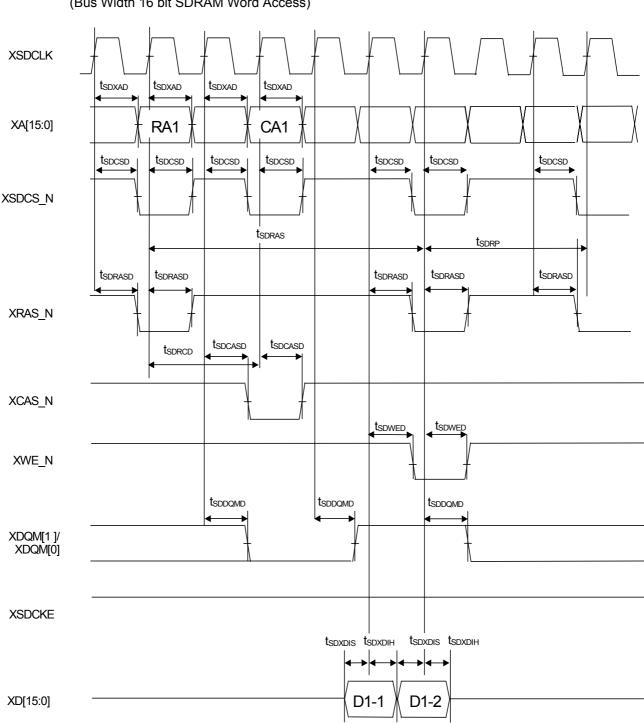

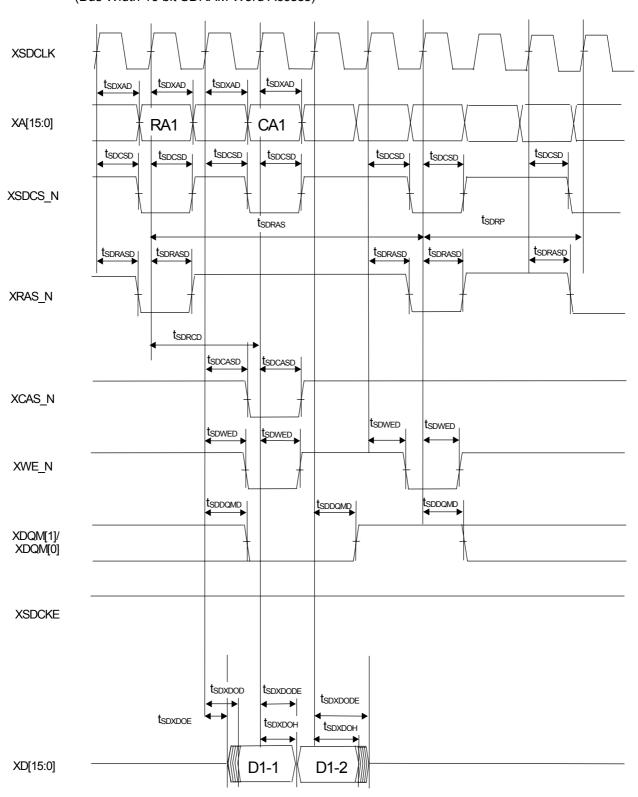

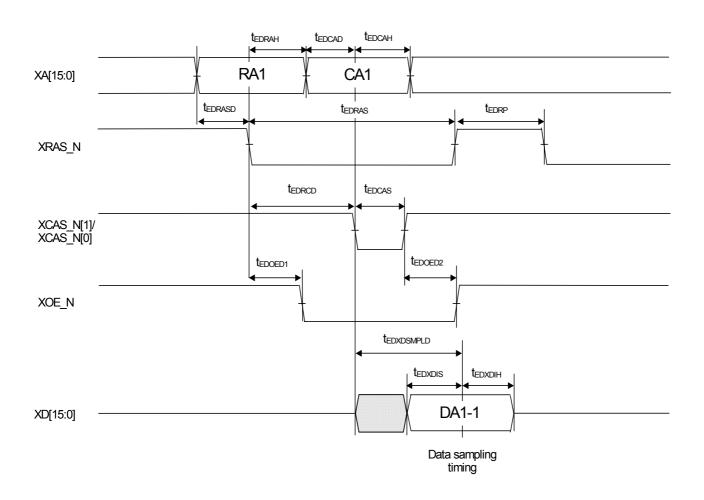

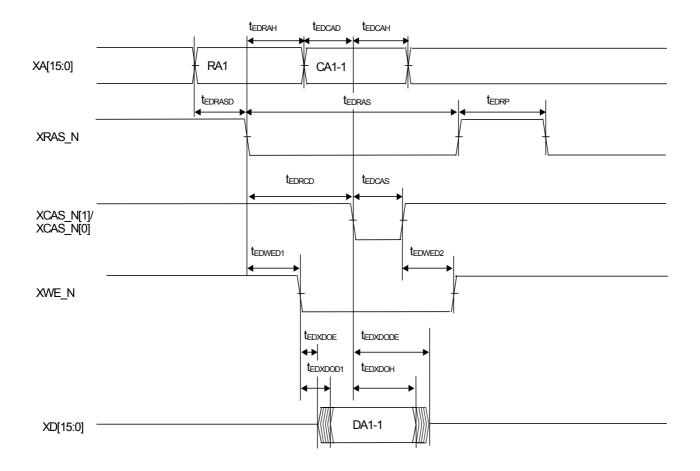

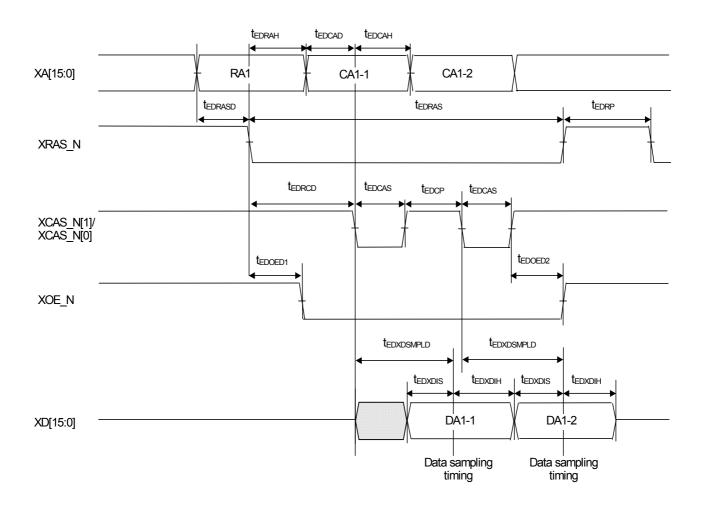

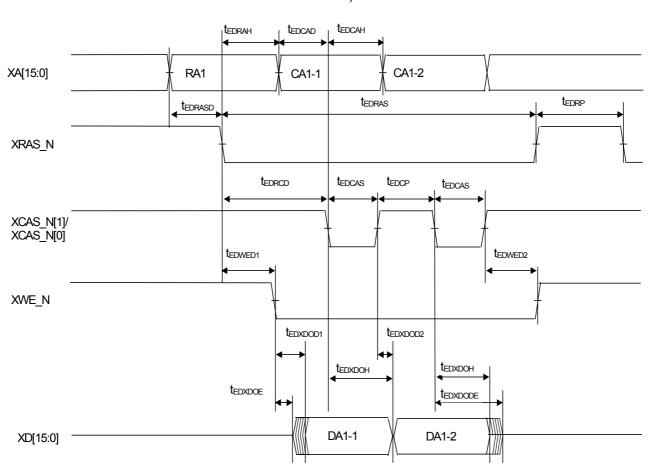

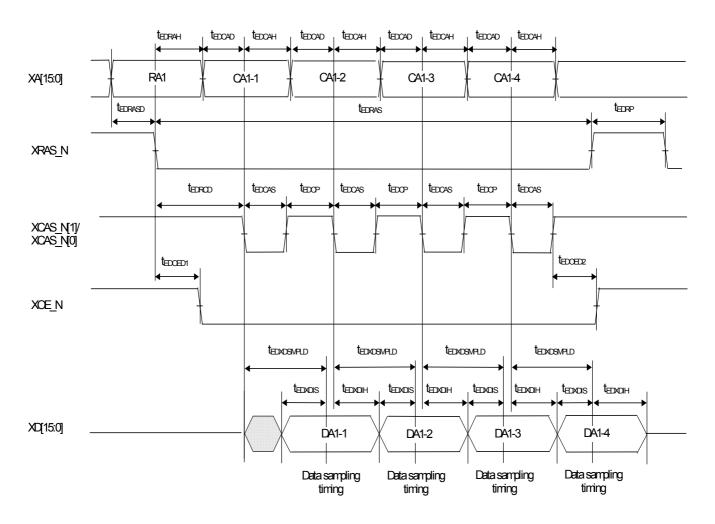

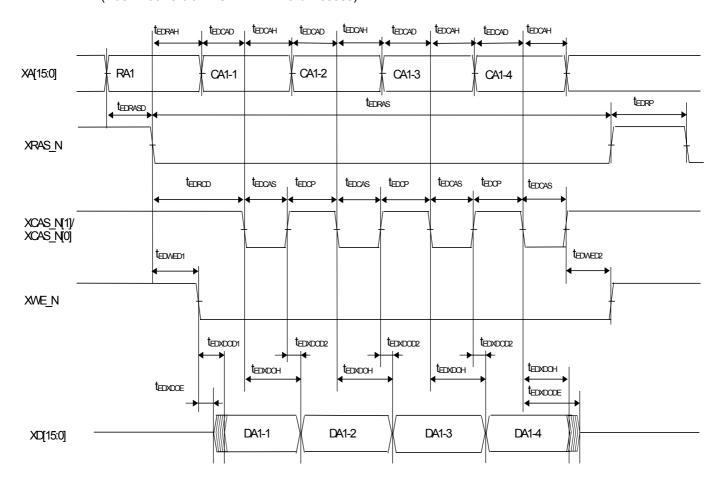

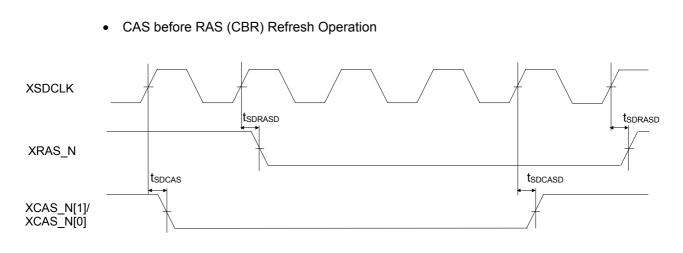

| 11.4.1  | .3 EDO DRAM Access                                                                    | 11-37 |

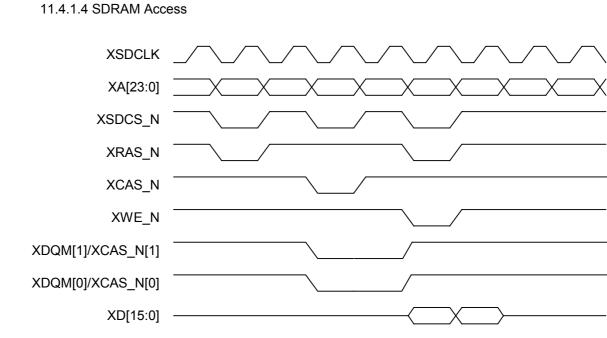

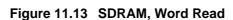

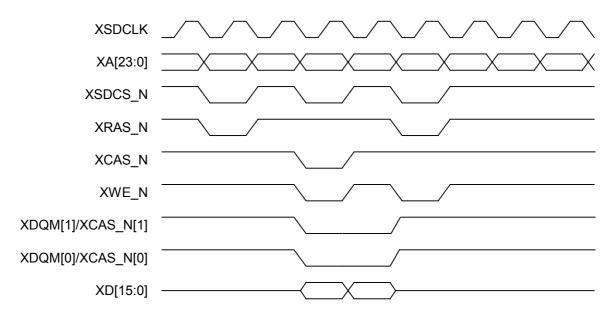

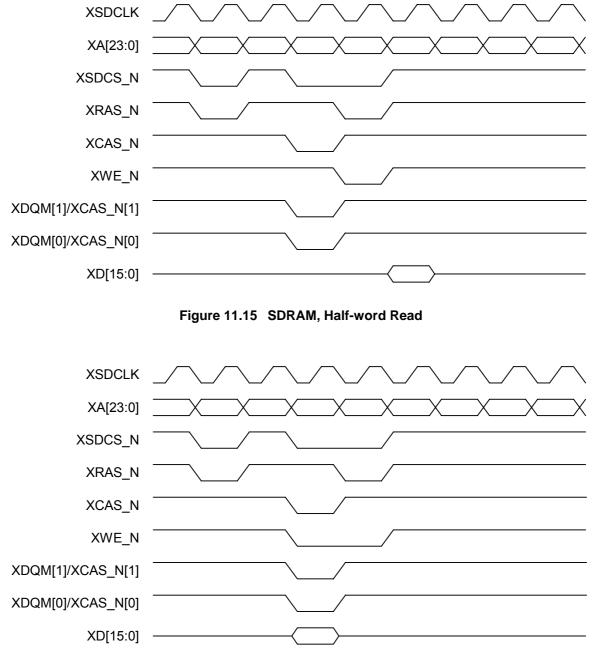

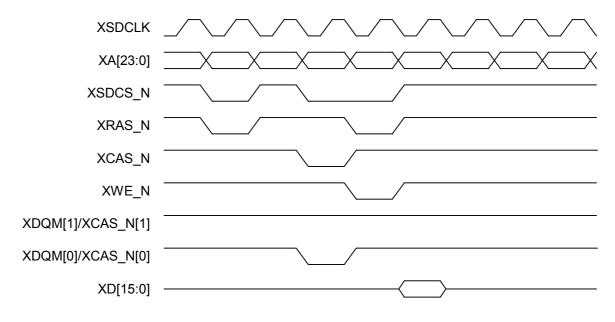

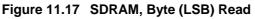

|         | .4 SDRAM Access                                                                       |       |

|         | AM Power Management                                                                   |       |

|         | mple External Memory Connections                                                      |       |

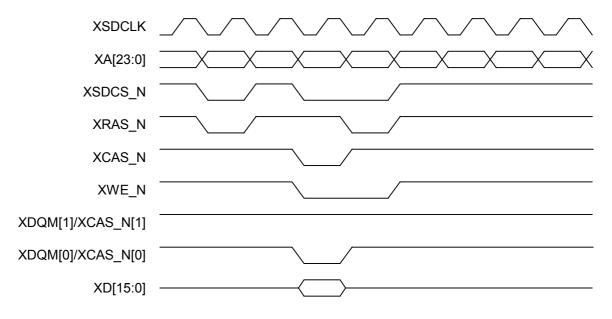

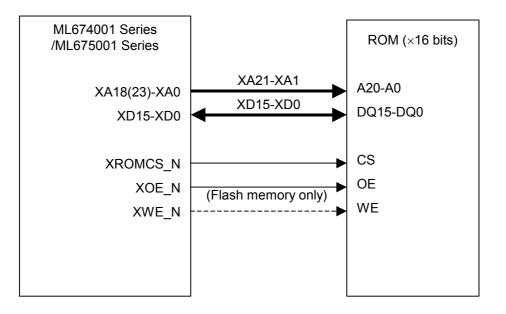

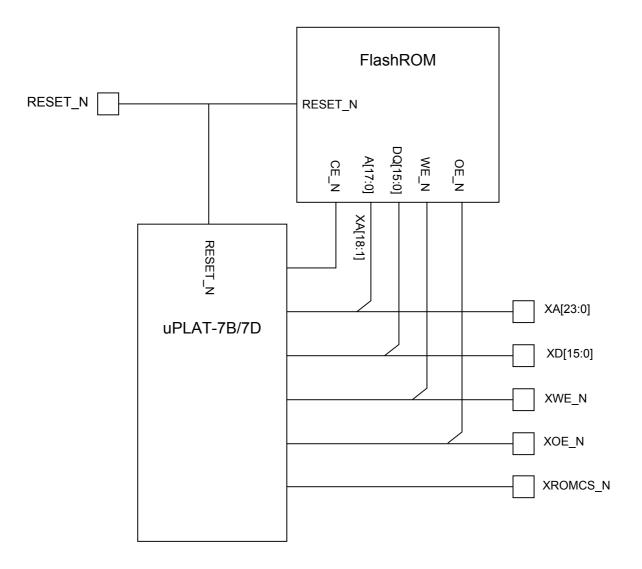

|         | Connecting ROM                                                                        |       |

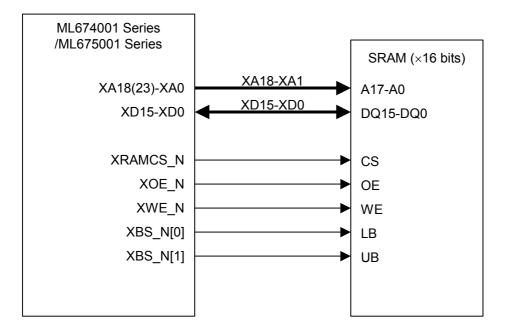

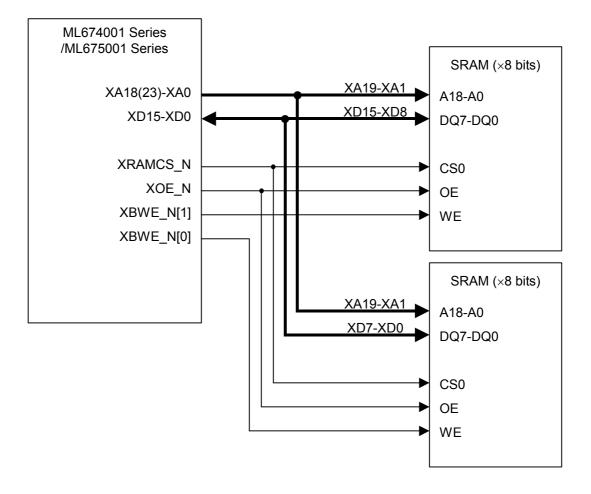

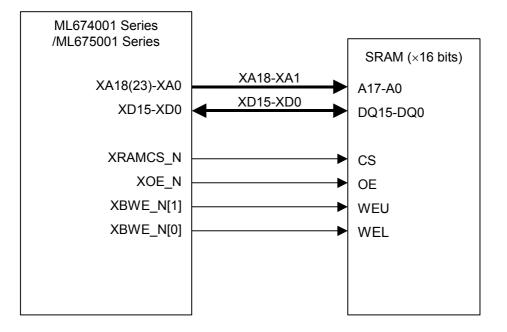

|         | Connecting SRAM                                                                       |       |

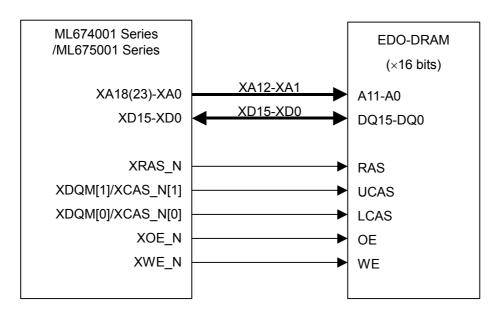

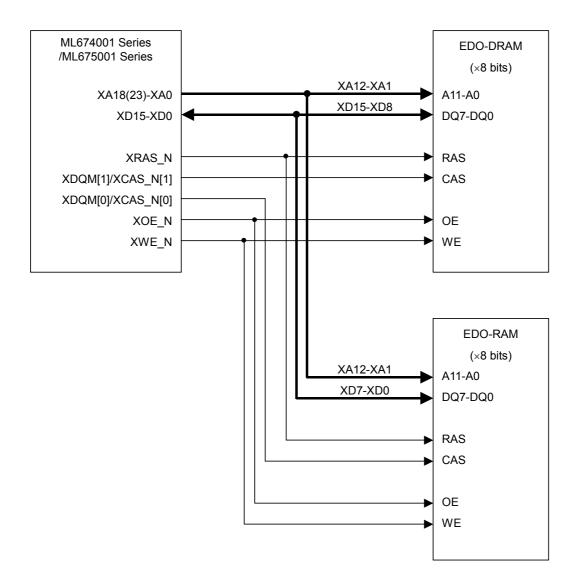

|         |                                                                                       |       |

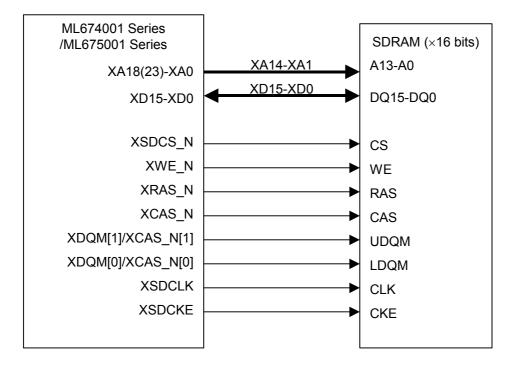

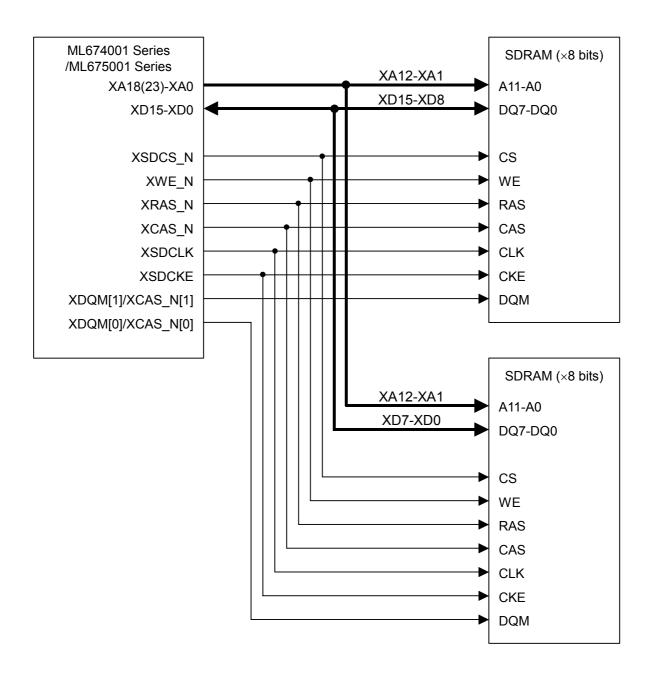

| 11.6.4  | Connecting SDRAM                                                                      | 11-50 |

## Chapter 12 Direct Memory Access Controller (DMAC)

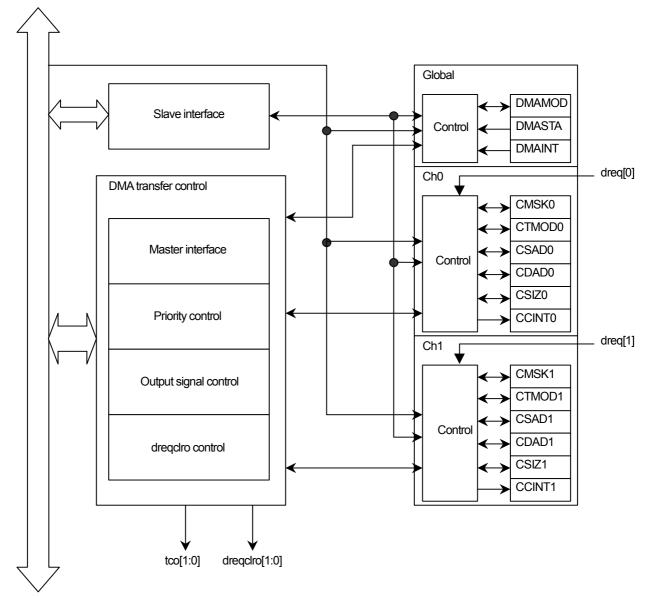

| 12.1 ( | Dverview                                                               |  |

|--------|------------------------------------------------------------------------|--|

| 12.1.1 | Components                                                             |  |

| 12.1.2 |                                                                        |  |

| 12.1.3 | Register List                                                          |  |

| 12.2 H | Register Descriptions                                                  |  |

| 12.2.1 | DMA Mode Register (DMAMOD)                                             |  |

| 12.2.2 | 2 DMA Status Register (DMASTA)                                         |  |

| 12.2.3 | B DMA Transfer Complete Status Register (DMAINT)                       |  |

| 12.2.4 | DMA Channel Mask Registers (DMACMSK0 and DMACMSK1)                     |  |

| 12.2.5 | 5 DMA Transfer Mode Registers (DMACTMOD0 and DMACTMOD1)                |  |

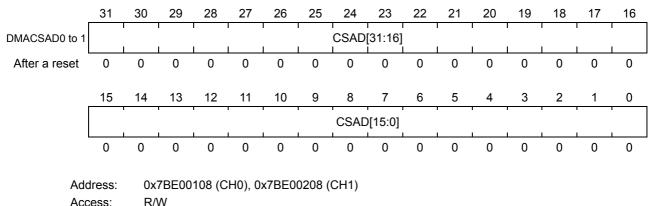

| 12.2.6 | 5 DMA Transfer Source Address Registers (DMACSAD0 and DMACSAD1)        |  |

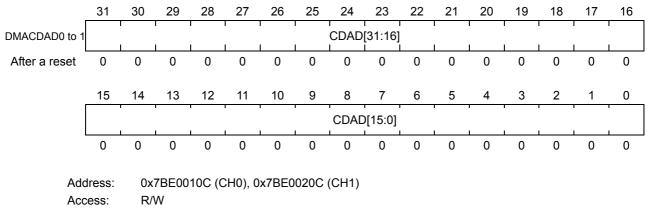

| 12.2.7 | DMA Transfer Destination Address Registers (DMACDAD0 and DMACDAD1)     |  |

| 12.2.8 | B DMA Transfer Count Registers (DMACSIZ0 and DMACSIZ1)                 |  |

| 12.2.9 | DMA Transfer Complete Status Clear Registers (DMACCINT0 and DMACCINT1) |  |

| 12.3 ( | Derational Description                                                 |  |

| 12.3.1 | DMA Transfer Modes                                                     |  |

| 12.3.2 | 2 DMA Request Sources                                                  |  |

| 12.3.3 | S Starting a DMA Transfer                                              |  |

| 12.3.4 | Ending a DMA Transfer                                                  |  |

| 12.3.5 | 5 DMA Channel Priority                                                 |  |

| 12.3.6 | 5 Important Usage Notes                                                |  |

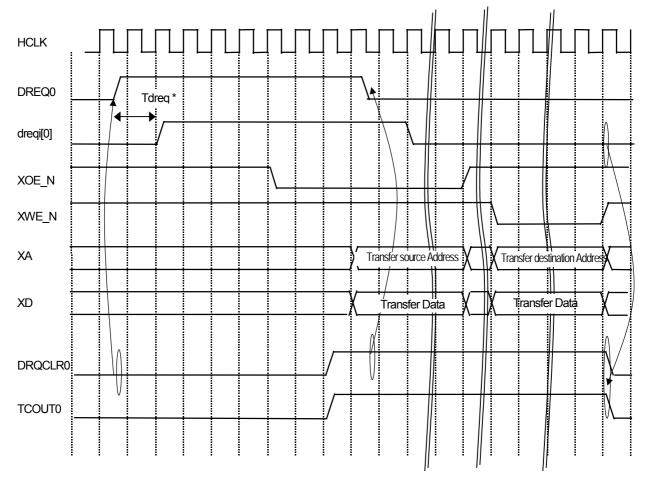

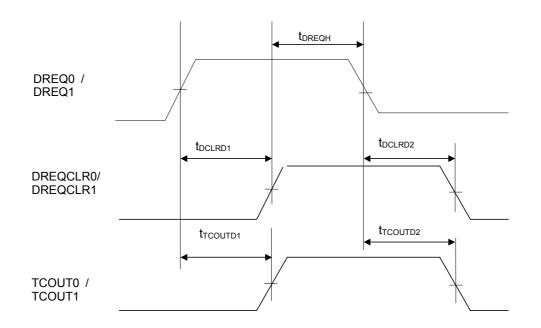

| 12.4 I | DMA Transfer Timing                                                    |  |

| 12.4.1 | $\partial$                                                             |  |

| 12.4.2 | 2 Transfer Timing                                                      |  |

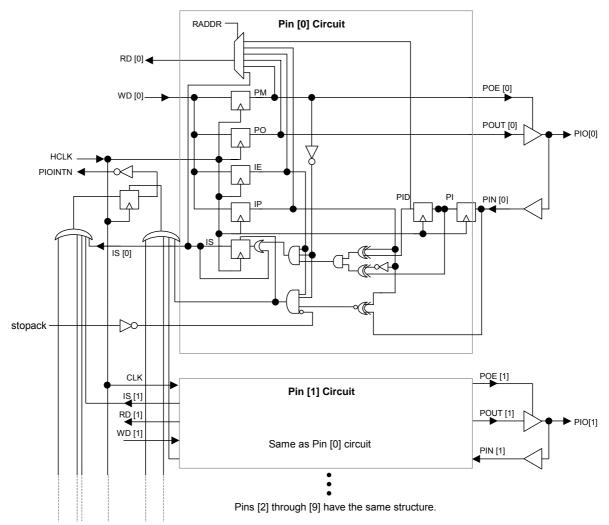

## Chapter 13 GPIO

| 13.1 O | verview                                                                 |  |

|--------|-------------------------------------------------------------------------|--|

| 13.1.1 | Components                                                              |  |

| 13.1.2 | Pin List                                                                |  |

| 13.1.3 | Register List                                                           |  |

| 13.2 R | egister Descriptions                                                    |  |

| 13.2.1 | Port Output Registers (GPPOA, GPPOB, GPPOC, GPPOD and GPPOE)            |  |

| 13.2.2 | Port Input Registers (GPPIA, GPPIB, GPPIC, GPPID, and GPPIE)            |  |

| 13.2.3 | Port Mode Registers (GPPMA, GPPMB, GPPMC, GPPMD and GPPME)              |  |

| 13.2.4 | Port Interrupt Enable Registers (GPIEA, GPIEB, GPIEC, GPIED and GPIEE)  |  |

| 13.2.5 | Port Interrupt Polarity Register (GPIPA, GPIPB, GPIPC, GPIPD and GPIPE) |  |

| 13.2.6 | Port Interrupt Status Registers (GPISA, GPISB, GPISC, GPISD and GPISE)  |  |

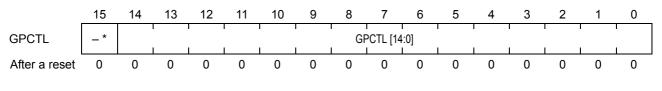

| 13.2.7 | Port Function Select Register (GPCTL)                                   |  |

| 13.3 D | escription of Operation                                                 |  |

| 13.3.1 | Interrupt Requests                                                      |  |

| 13.3.2 | Primary/Secondary function configuration                                |  |

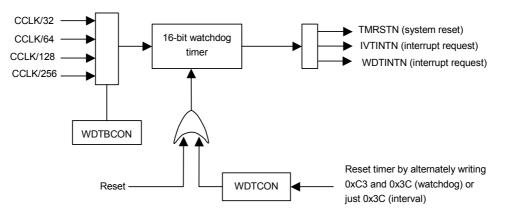

# Chapter 14 Watchdog Timer (WDT)

| 14.1 O  | verview                                      |  |

|---------|----------------------------------------------|--|

| 14.1.1  | Components                                   |  |

| 14.1.2  | Register List                                |  |

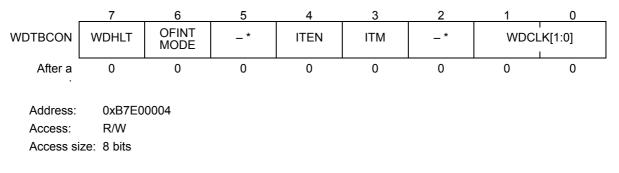

| 14.2 Re | egister Descriptions                         |  |

| 14.2.1  | Watchdog Timer Control Register (WDTCON)     |  |

| 14.2.2  | Time Base Counter Control Register (WDTBCON) |  |

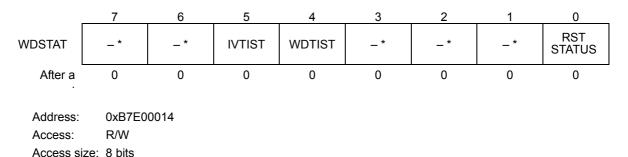

|         | Status Register (WDSTAT)                     |  |

| 14.3 De | escription of Operation                      |  |

| 14.3.1  | Operation Modes                              |  |

| 14.3.2 | Interval Timer Operation | 14-6 |

|--------|--------------------------|------|

|        | Watchdog Timer Operation |      |

| 14.3.4 | Starting Timer           | 14-6 |

# Chapter 15 Timers

| 15.1 Ov | verview                                          |      |

|---------|--------------------------------------------------|------|

| 15.1.1  | Components                                       | 15-1 |

| 15.1.2  | Register List                                    |      |

| 15.2 Re | gister Descriptions                              |      |

| 15.2.1  | System Timer Enable Register (TMEN)              |      |

| 15.2.2  | System Timer Reload Register (TMRLR)             |      |

| 15.2.3  | System Timer Overflow Register (TMOVFR)          |      |

| 15.2.4  | Timer Control Registers (TIMECNTL0 to TIMECNTL5) |      |

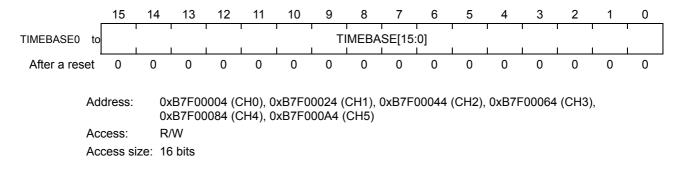

| 15.2.5  | Timer Base Registers (TIMEBASE0 to TIMEBASE5)    |      |

| 15.2.6  | Timer Counter Register (TIMECNT0 to TIMECNT5)    |      |

| 15.2.7  | Timer Compare Registers (TIMECMP0 to TIMECMP5)   |      |

| 15.2.8  | Timer Status Registers (TIMESTAT0 to TIMESTAT5)  |      |

| 15.3 De | escription of Operation                          |      |

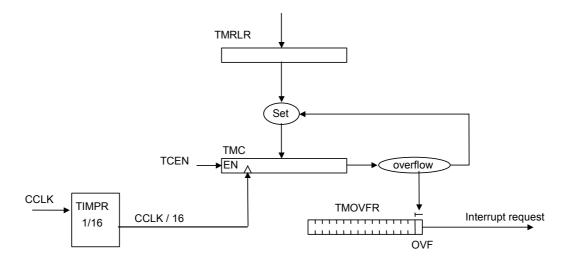

| 15.3.1  | System Timer                                     |      |

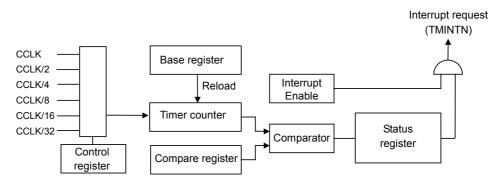

| 15.3.2  | Auto Reload Timers                               |      |

| 15.3.3  | Specifying Clock and Starting Auto Reload Timers |      |

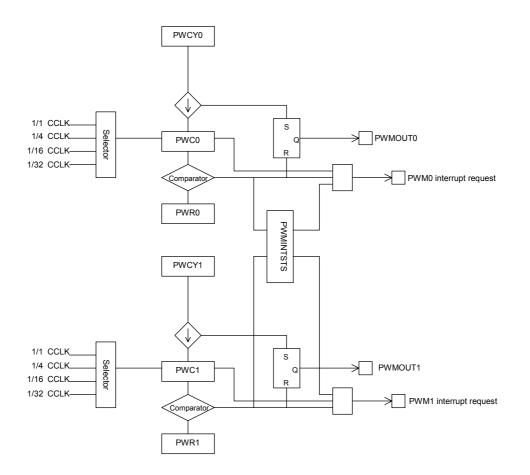

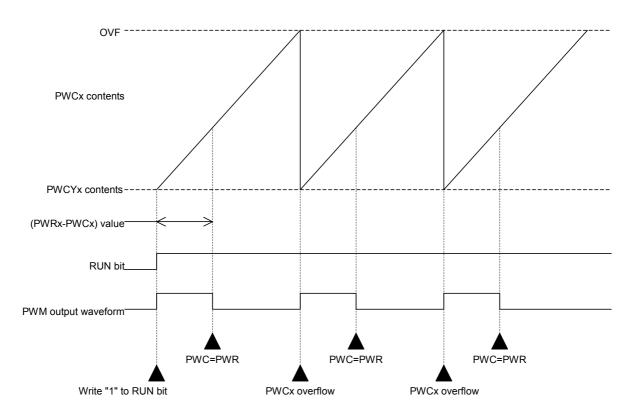

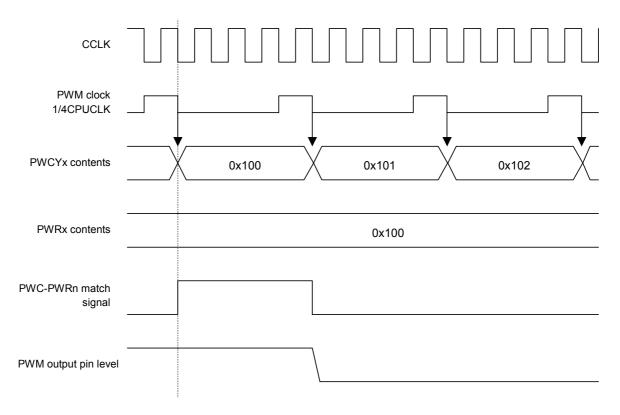

# Chapter 16. PWM Generator

| 16.1 | Overview                                      |  |

|------|-----------------------------------------------|--|

| 16.1 | .1 Components                                 |  |

| 16.1 | .2 Pin List                                   |  |

| 16.1 | .3 Register List                              |  |

| 16.2 | Register Descriptions                         |  |

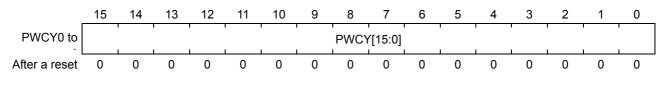

| 16.2 | 2.1 PWM Registers (PWR0 and PWR1)             |  |

| 16.2 | 2.2 PWM Period Registers (PWCY0 and PWCY1)    |  |

| 16.2 | PWM Counter (PWC0 and PWC1)                   |  |

| 16.2 | 2.4 PWM Control Registers (PWCON0 and PWCON1) |  |

| 16.2 | 2.5 PWM Interrupt Status Register (PWINTSTS)  |  |

| 16.3 | Description of Operation                      |  |

| 16.3 | 8.1 PWM Operation                             |  |

| 16.3 | 3.2 Timing Examples                           |  |

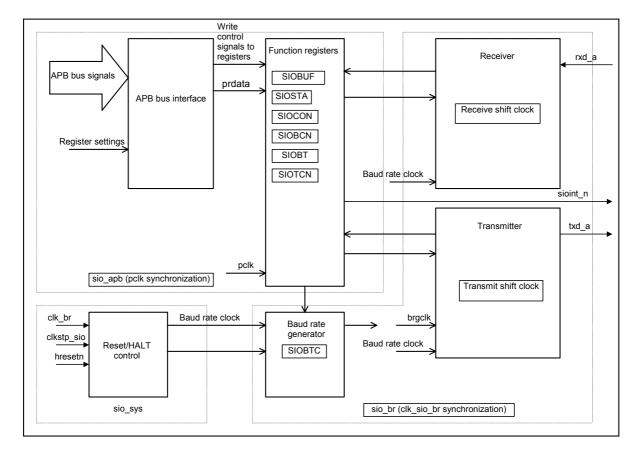

# Chapter 17 SIO

| 17.1 Ov | verview                             |  |

|---------|-------------------------------------|--|

| 17.1.1  | Components                          |  |

| 17.1.2  | Pin List                            |  |

| 17.1.3  | Control Register List               |  |

| 17.2 Co | ontrol Register Descriptions        |  |

|         | Transfer Buffer Register (SIOBUF)   |  |

| 17.2.2  | SIO Status Register (SIOSTA)        |  |

| 17.2.3  | SIO Control Register (SIOCON)       |  |

| 17.2.4  | Baud Rate Control Register (SIOBCN) |  |

| 17.2.5  | Baud Rate Timer Register (SIOBT)    |  |

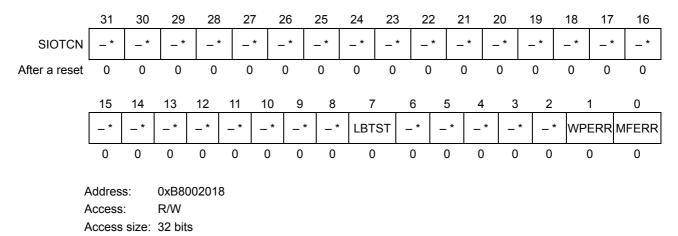

| 17.2.6  | SIO test control Register (SIOTCN)  |  |

| 17.3 De | escription of Operation             |  |

|         | Transmitting Data                   |  |

| 17.3.2  | Receiving Data                      |  |

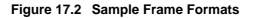

| 17.3.3  | Generating Baud Rate Clock          |  |

| 17.3.4  | Receive Interrupts                  |  |

|         | -                                   |  |

| 17.3 | 5 Transmit Interrupts1 | 7- | 1. | 3 |

|------|------------------------|----|----|---|

| 17.4 | Important Usage Notes1 | 7- | 14 | 4 |

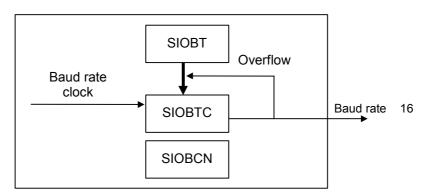

# Chapter 18 UART with FIFO(16byte)

| 18.1 Ov | /erview                                     |  |

|---------|---------------------------------------------|--|

| 18.1.1  | Components                                  |  |

| 18.1.2  | Pins                                        |  |

| 18.1.3  | Register List                               |  |

| 18.2 Re | gister Descriptions                         |  |

| 18.2.1  | Receiver Buffer Register (UARTRBR)          |  |

| 18.2.2  | Transmitter Holding Register (UARTTHR)      |  |

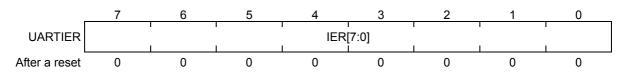

| 18.2.3  | Interrupt Enable Register (UARTIER)         |  |

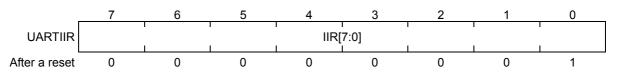

| 18.2.4  | Interrupt Identification Register (UARTIIR) |  |

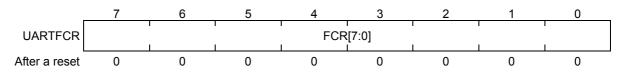

| 18.2.5  | FIFO Control Register (UARTFCR)             |  |

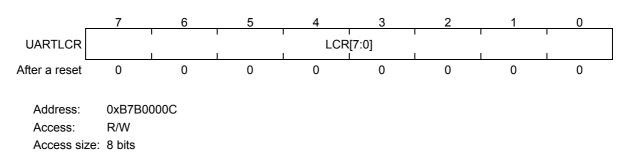

| 18.2.6  | Line Control Register (UARTLCR)             |  |

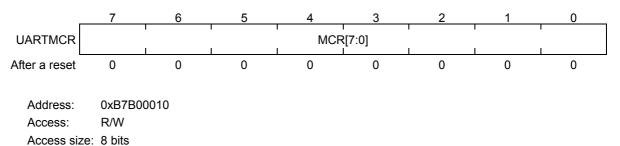

| 18.2.7  | Modem Control Register (UARTMCR)            |  |

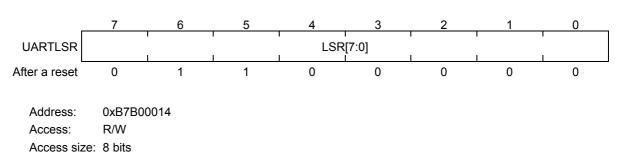

| 18.2.8  | Line Status Register (UARTLSR)              |  |

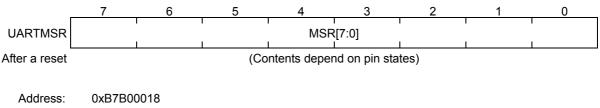

| 18.2.9  | Modem Status Register (UARTMSR)             |  |

| 18.2.10 | Scratch Register (UARTSCR)                  |  |

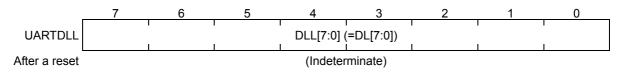

| 18.2.11 | Divisor Latch (LSB) (UARTDLL)               |  |

| 18.2.12 | Divisor Latch (MSB) (UARTDLM)               |  |

| 18.3 De | escription of Operation                     |  |

| 18.3.1  | Transmitting Data                           |  |

| 18.3.2  | Receiving Data                              |  |

| 18.3.3  | Generating Baud Rate Clock                  |  |

| 18.3.4  | Buffered Operation                          |  |

| 18.3.5  | Queue Polled Mode                           |  |

| 18.3.6  | Error Status                                |  |

| 18.3.7  | Setup Procedure                             |  |

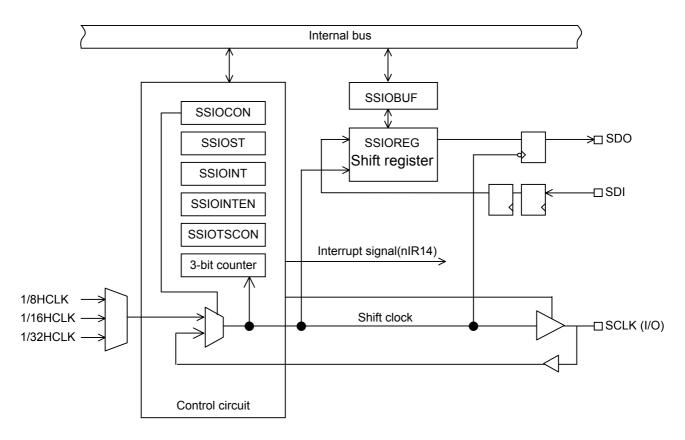

# Chapter 19 Synchronous SIO

| 19.1 Ove | erview                                                     |  |

|----------|------------------------------------------------------------|--|

| 19.1.1   | Configuration                                              |  |

|          | List of Pins                                               |  |

| 19.1.3   | List of Registers                                          |  |

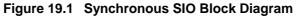

|          | zisters                                                    |  |

|          | Synchronous SIO Transmit/Receive Buffer Register (SSIOBUF) |  |

| 19.2.2   | Synchronous SIO Status Register (SSIOST)                   |  |

| 19.2.3   | Synchronous SIO Interrupt Request Register (SSIOINT)       |  |

| 19.2.4   | Synchronous SIO Interrupt Enable Register (SSIOINTEN)      |  |

| 19.2.5   | Synchronous SIO Control Register (SSIOCON)                 |  |

| 19.2.6   | Synchronous SIO Test Control Register (SSIOTSCON)          |  |

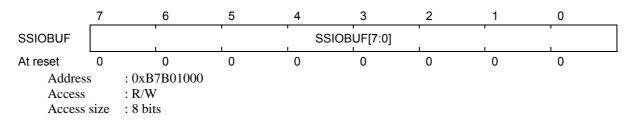

| 19.3 Ope | erations                                                   |  |

| 19.3.1   | Master Mode/Slave Mode                                     |  |

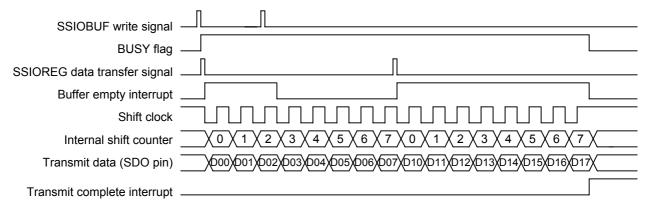

| 19.3.2   | Transmit Operation                                         |  |

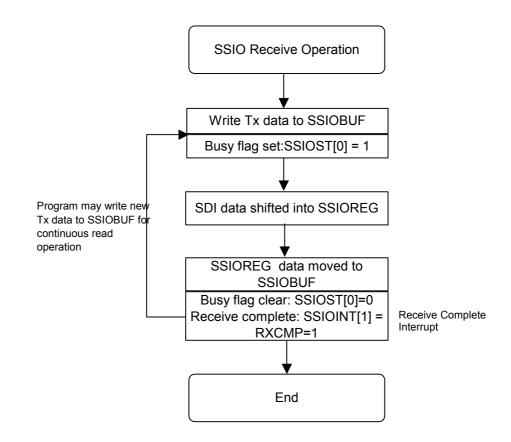

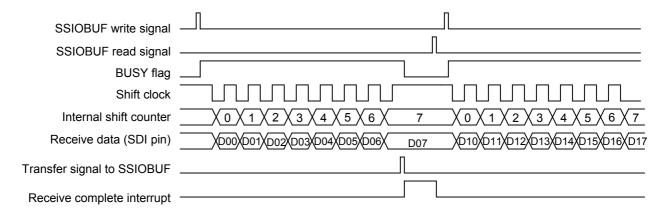

| 19.3.3   | Receive Operation                                          |  |

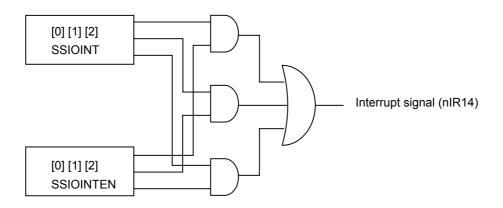

| 19.3.4   | Interrupt Signal                                           |  |

|          |                                                            |  |

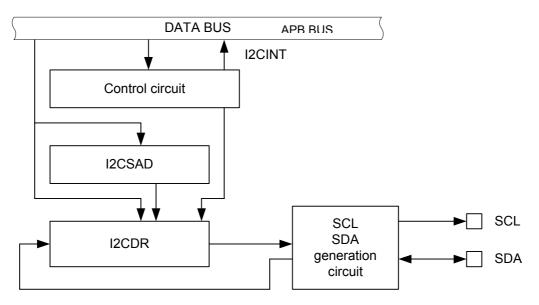

# Chapter 20 I2C

| 20.1 Ove | erview            |  |

|----------|-------------------|--|

|          | Configuration     |  |

|          | List of Pins      |  |

|          | List of Registers |  |

|          | risters           |  |

| 8        |                   |  |

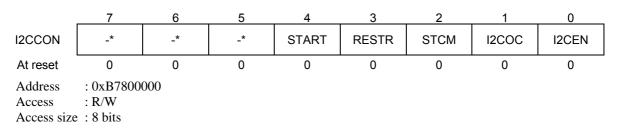

| 20.2.1  | I2C Bus Control Register (I2CCON)                                                            | 20-3  |

|---------|----------------------------------------------------------------------------------------------|-------|

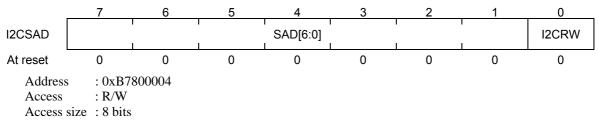

| 20.2.2  | I2C Bus Slave Address Mode Register (I2CSAD)                                                 |       |

| 20.2.3  | I2C Bus Transfer Speed Register (I2CCLR)                                                     |       |

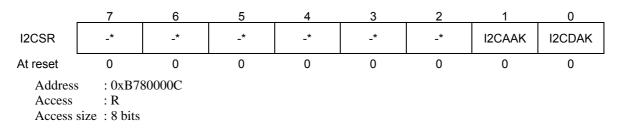

| 20.2.4  | I2C Bus Status Register (I2CSR)                                                              |       |

| 20.2.5  | I2C Bus Interrupt Request Register (I2CIR)                                                   |       |

| 20.2.6  | I2C Bus Interrupt Mask Register (I2CIMR)                                                     |       |

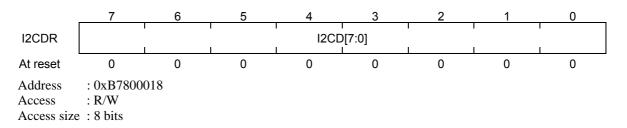

| 20.2.7  | I2C Bus Transmit/Receive Data Register (I2CDR)                                               | 20-10 |

| 20.2.8  | I2C Bus Transfer Speed Counter (I2CBC)                                                       | 20-11 |

| 20.3 Op | perations                                                                                    | 20-12 |

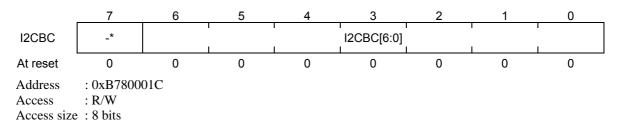

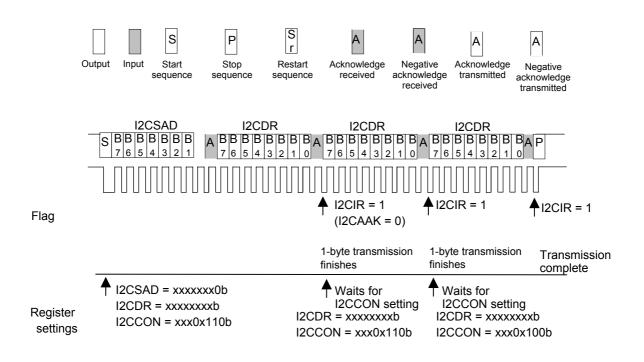

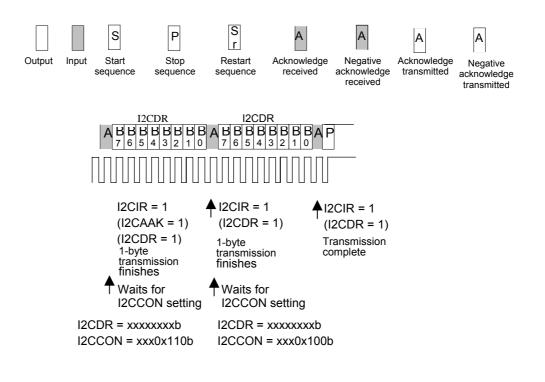

| 20.3.1  | Transmit operation (transfer of 1 byte from master to slave, in 7-bit address mode)          | 20-12 |

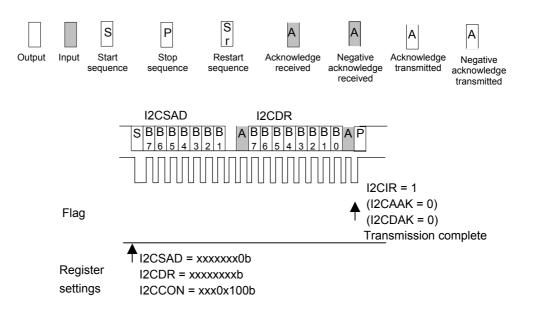

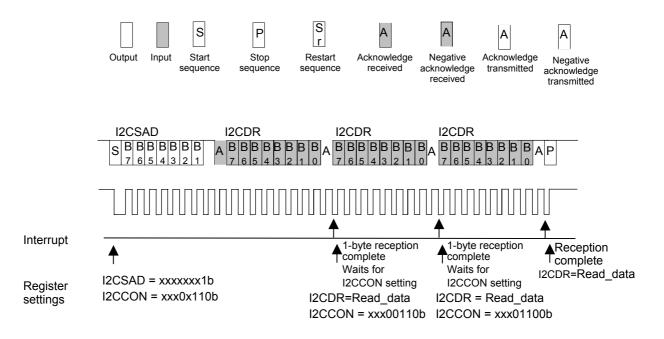

| 20.3.2  | Receive operation (transfer of 1 byte from slave to master, in 7-bit address mode)           | 20-13 |

| 20.3.3  | Transmit operation (transfer of 2 or more bytes from master to slave, in 7-bit address mode) | 20-14 |

| 20.3.4  | Receive operation (transfer of 2 byte or more from slave to master, in 7-bit address mode)   | 20-15 |

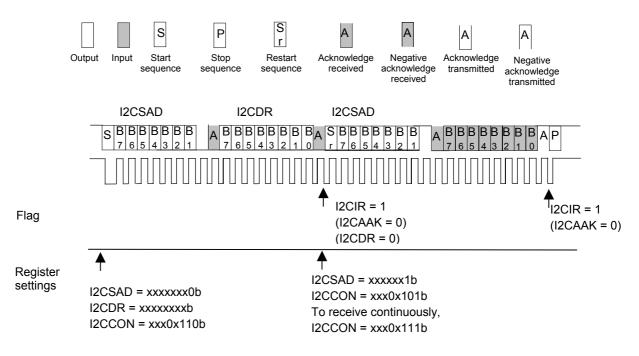

| 20.3.5  | Restart sequence transmit operation                                                          | 20-16 |

| 20.3.6  | To receive 1-byte of data from another slave device after transmitting 1-byte of data:       | 20-16 |

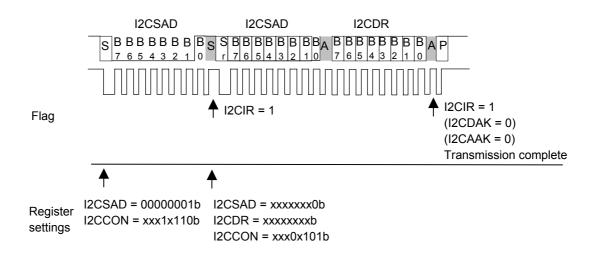

| 20.3.7  | Start byte transmit operation                                                                | 20-17 |

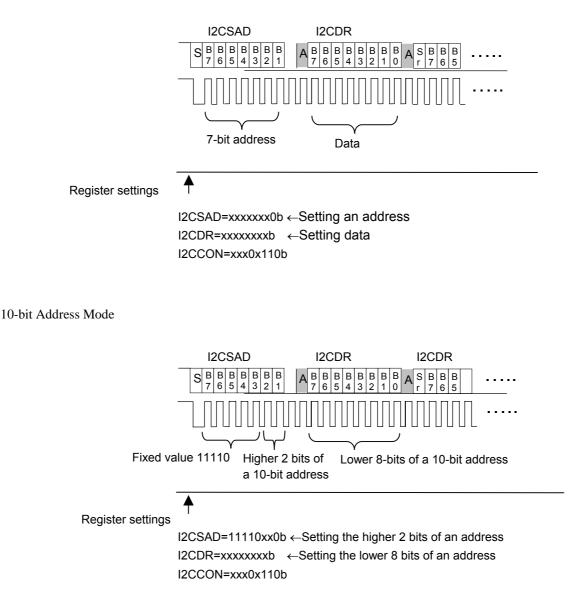

| 20.3.8  | 7-bit Address Mode and 10-bit Address Mode                                                   | 20-19 |

# Chapter 21 Analog-to-Digital Converter

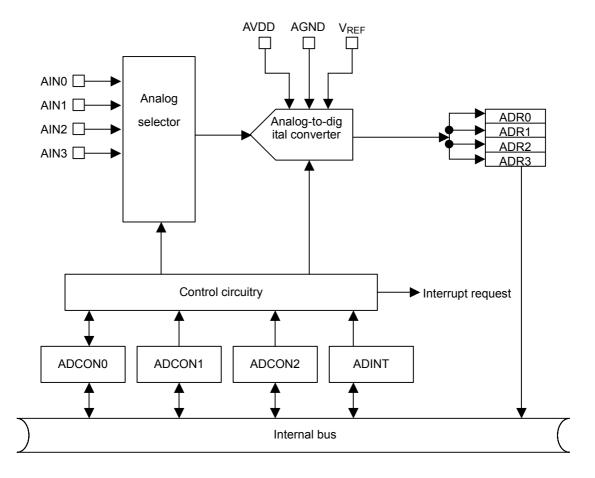

| 21.1 Ov | verview                                                        |  |

|---------|----------------------------------------------------------------|--|

| 21.1.1  | Components                                                     |  |

| 21.1.2  | Pin List                                                       |  |

| 21.1.3  | Control Register List                                          |  |

|         | ontrol Register Descriptions                                   |  |

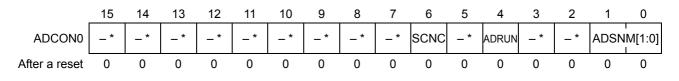

| 21.2.1  | Analog-to-Digital Converter Control Register 0 (ADCON0)        |  |

| 21.2.2  | Analog-to-Digital Converter Control Register 1 (ADCON1)        |  |

| 21.2.3  | Analog-to-Digital Converter Control Register 2 (ADCON2)        |  |

| 21.2.4  | Analog-to-Digital Converter Interrupt Control Register (ADINT) |  |

| 21.2.5  | Analog-to-Digital Converter Forced Interrupt Register (ADFINT) |  |

| 21.2.6  | Analog-to-Digital Converter Result Registers (ADR0 to ADR3)    |  |

| 21.3 Op | perational Description                                         |  |

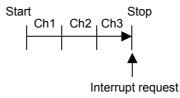

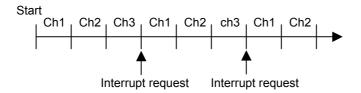

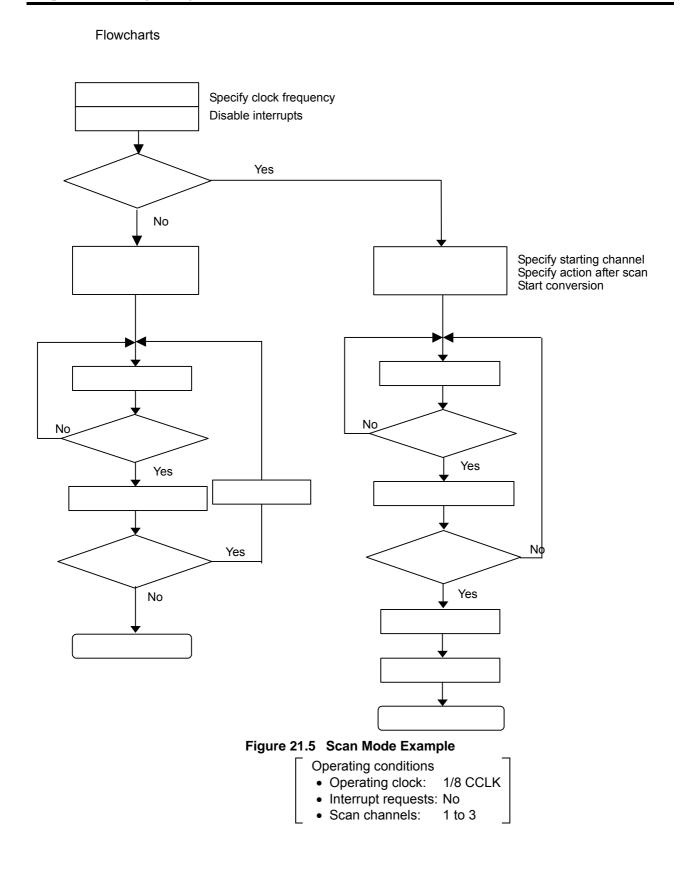

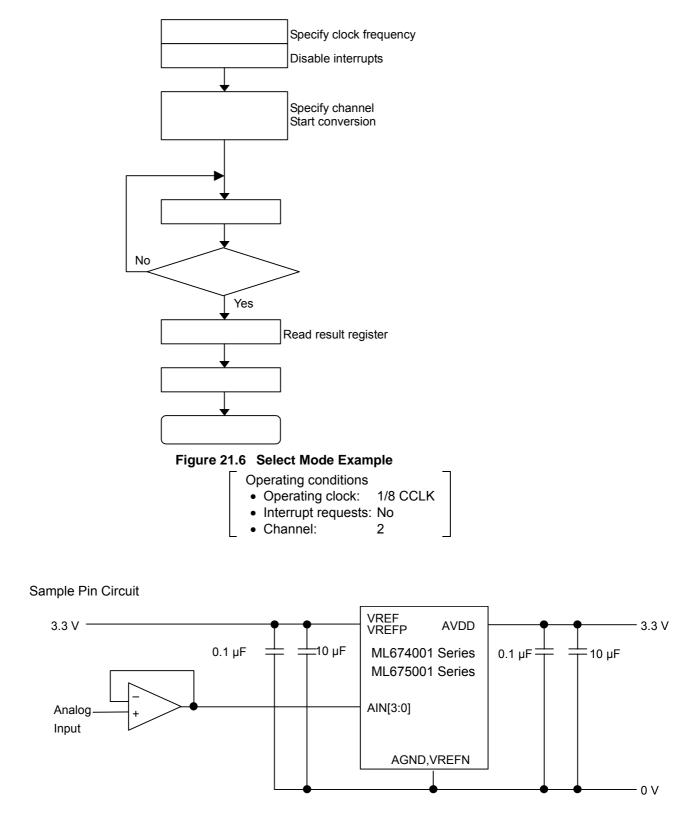

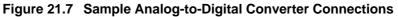

| 21.3.1  | Scan Mode                                                      |  |

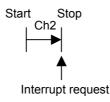

| 21.3.2  | Select Mode                                                    |  |

|         |                                                                |  |

# Chapter 22 Built-In Flash Memory

| 22.1 Ov  | /erview                                                         |  |

|----------|-----------------------------------------------------------------|--|

| 22.1.1   | Block Diagram                                                   |  |

| 22.2 Fla | ash Memory Programming                                          |  |

| 22.2.1   | General Description of Flash Memory Programming                 |  |

| 22.2.2   | Flash Memory Programming Method Using the JTAG Debug Function   |  |

| 22.2.3   | Flash Memory Programming Method Using the Built-in Boot Program |  |

| 22.3 Bu  | ıilt-in Boot Program                                            |  |

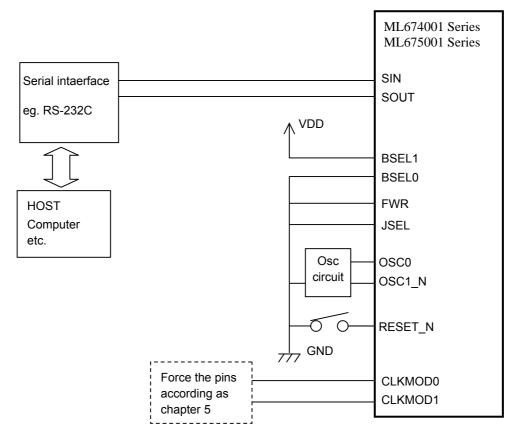

| 22.3.1   | Functional Description                                          |  |

| 22.3.2   | Operating Procedure                                             |  |

| 22.3.3   | Operating Environment                                           |  |

| 22.4 SE  | DP Command Sequence Control for Built-In Flash Memory           |  |

| 22.4.1   | Operational Description                                         |  |

| 22.4.2   | Command Entries                                                 |  |

| 22.4.3   | Read/Reset (Software Reset)                                     |  |

| 22.4.4   | Erase                                                           |  |

| 22.4.5   | Program                                                         |  |

| 22.4.6   | Protect                                                         |  |

| 22.4.7   | Protect Cancel                                                  |  |

| 22.4.8   | Product Identification/Software ID                              |  |

|          |                                                                 |  |

| 22.4.9 Verify Protect                                  |  |

|--------------------------------------------------------|--|

| 22.4.10 Hardware Reset                                 |  |

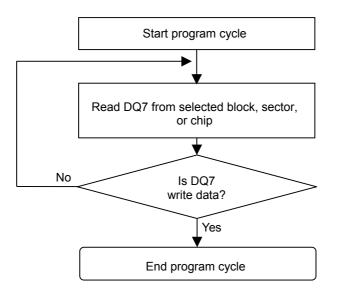

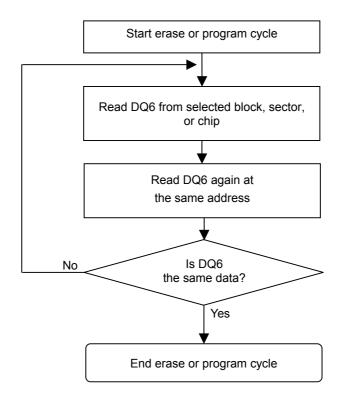

| 22.4.11 Detecting the End of an Erase or Program Cycle |  |

# Chapter 23 JTAG

| 23.1 0 | /erview                       | 23-1 |

|--------|-------------------------------|------|

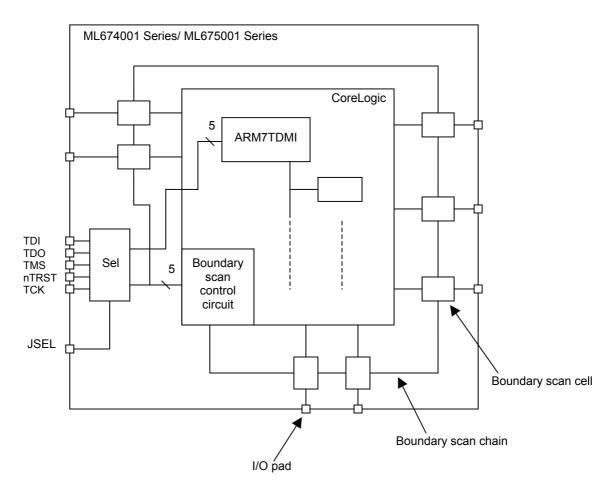

|        | Configuration                 |      |

|        | Pin List                      |      |

|        | n-Board Debug Function        |      |

|        | Necessary Conditions          |      |

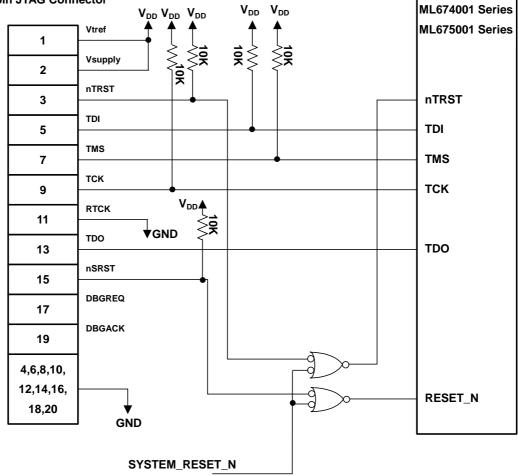

|        | Connections                   |      |

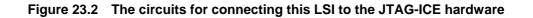

|        | bundary Scan Function         |      |

|        | Boundary Scan Control Circuit |      |

|        | Registers                     |      |

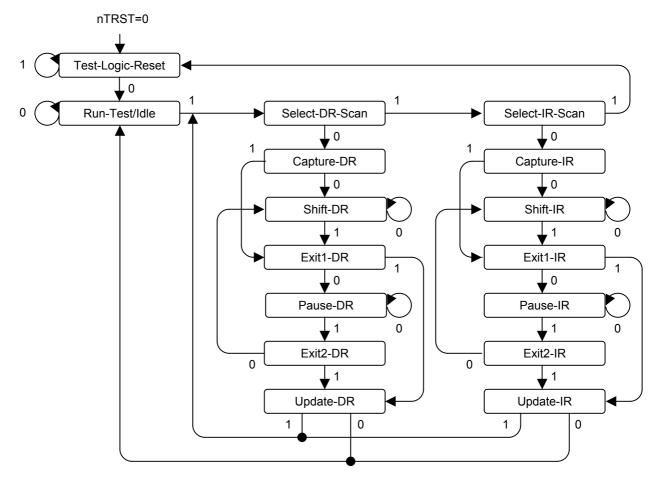

|        | TAP Controller                |      |

| 23.3.4 | Instructions                  |      |

|        |                               |      |

## **Chapter 24 Electrical Characteristics**

| 24.1 Absolute Maximum Ratings                    |  |

|--------------------------------------------------|--|

| 24.2 Operating Conditions                        |  |

| 24.3 Electrical Characteristics                  |  |

| 24.3.1 DC Characteristics for ML674001 Series    |  |

| 24.3.2 DC Characteristics for ML675001 Series    |  |

| 24.4 AC Characteristics                          |  |

| 24.4.1 AC Characteristics for ML674001 Series    |  |

| 24.4.2 AC Characteristics for ML675001 Series    |  |

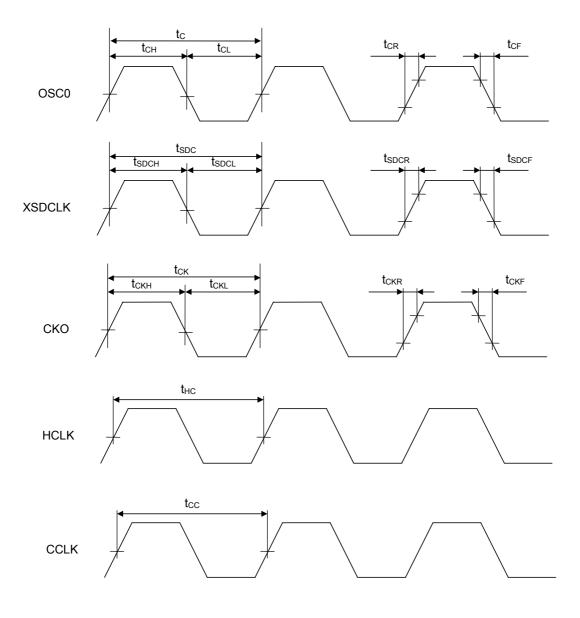

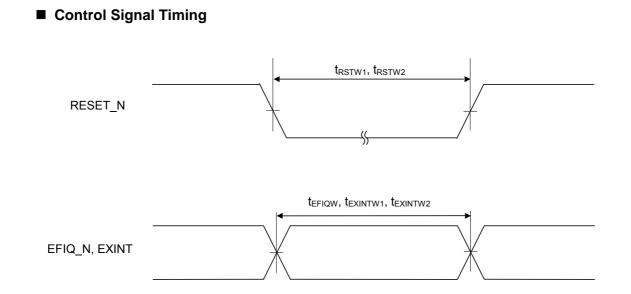

| 24.4.3 Timing Charts                             |  |

| 24.5 Analog-to-Digital Converter Characteristics |  |

# Appendixes

| Appendix A. | Register List A-1      |

|-------------|------------------------|

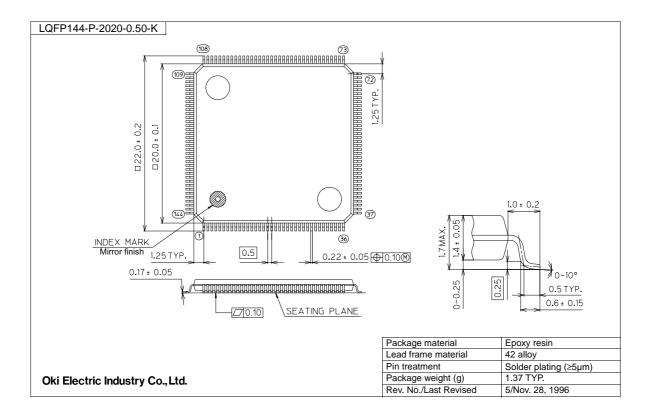

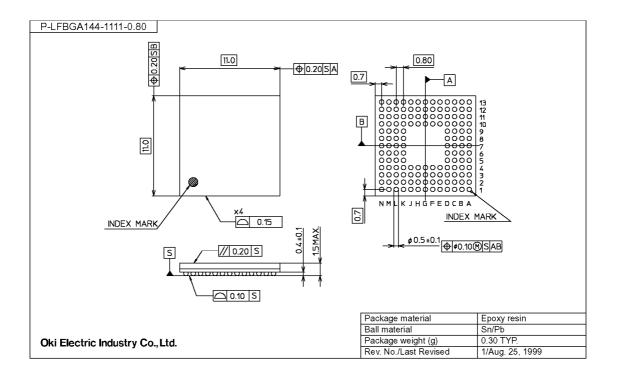

| Appendix B. | Package Dimensions A-6 |

# **Revision History**

| Revision History | R-1 |

|------------------|-----|

|------------------|-----|

\_\_\_\_\_

Chapter 1

# Introduction

# Chapter 1 Introduction

### 1.1 Features

This high-performance CMOS 32-bit micro-controller combines the 32-bit ARM7TDMI<sup>™</sup> core, a RISC CPU developed by Advanced RISC Machines Limited (ARM), with a DMA controller, serial ports, PWM generator, analog-to-digital converter, 16-bit timers, and other peripheral functions on a single LSI.

In addition to 32-bit data processing, this LSI includes internal RAM and onboard peripherals that make it ideal for such embedded control applications as PC peripherals and communication terminals.

Finally, there is a built-in external memory controller for directly connecting ROM, SRAM, SDRAM, other memory types, and peripheral devices.

The following is a list of features.

- CPU

- 32-bit RISC CPU (ARM7TDMI)

- Built-in 8KB unified cache (ML675001 series only)

- Little endian byte order

- Operating frequency: ML674001 series :1 MHz to 33 MHz ML675001 series :1 MHz to 60 MHz

- Instruction set: Free switching between a highly dense 32-bit instruction set and a 16-bit subset offering higher object code efficiency

- General-purpose registers: 32-bit × 31

- Barrel shifter: Simultaneous ALU and barrel shift operations in the same instruction

- Multiplier (32-bit  $\times$  8-bit)

- JTAG interface for debugging

- Built-in Memory

- SRAM 32Kbytes (8K x 32bits), 1 cycle access

- FLASH memory

- ML674001: ROM-less version

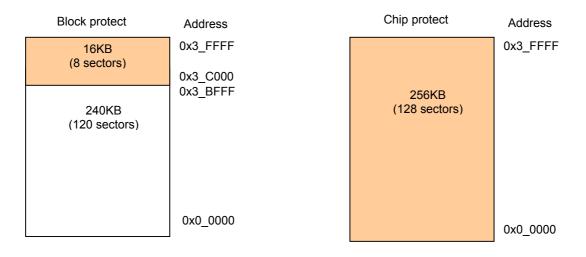

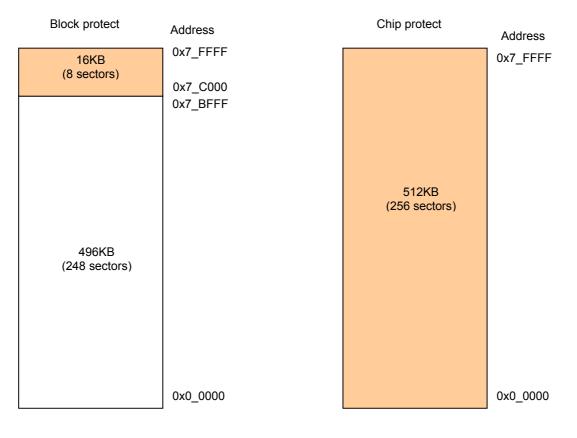

ML67Q4002: 256Kbytes (128K x 16bits)

ML67Q4003: 512Kbytes (256K x 16bits)

- ML675001: ROM-less version

- ML67Q5002: 256Kbytes (128K x 16bits)

- ML67Q5003: 512Kbytes (256K x 16bits)

- Interrupt Controller

- One fast interrupt (FIQ) source (external)

- 27 interrupt (IRQ) sources (23 internal and 4 external)

- Independent masking for each FIQ and IRQ source

- Independent interrupt priority level settings for each IRQ source

- Priority control blocking IRQ requests with priority levels at or below those for interrupt requests currently being processed

- Choice of level or edge sensing for external IRQ sources EXINT0 to EXINT3.

- Timers

- One 16-bit system timer

- Six 16-bit auto reload timers

Independent clock settings for each timer

Independent choice of one shot or interval timer operation for each timer

Maximum period: 30 ms or more

- Watchdog Timer

- One 16-bit timer

- Choice of interval or watchdog timer operation

- Choice of interrupt or reset upon overflow

- Maximum period: 200 ms or more

- GPIO

- Four 8-bit ports

- One 10-bit port

- Individual settings for pin I/O direction

- Individual settings for pin interrupt requests

- PWM

- Two outputs with 16-bit resolution

- Maximum period; 30 ms or more

- Analog-to-Digital Converter

- Four channels of 10-bit resolution, each using consecutive comparison

- Sample and hold function

- Choice of scan or select operation

- Conversion time:

- ML674001 series :5 µs to 25 µs

- ML675001 series :2 µs to 25 µs

- DMA Controller

- Two channels

- Choice of fixed or round robin mode for channel priority order

- Choice of cycle-steal or burst mode for requesting bus access

- Choice of software or external DMA transfer requests

- Maximum transfer count: 65,536

- Data transfer sizes: 8-, 16-, and 32-bit

- External Memory Controller

- ROM access

- Supports 16-bit devices

- Supports Flash memory

- SRAM access

- Supports 16-bit devices

- Supports Asynchronous SRAM

- DRAM access

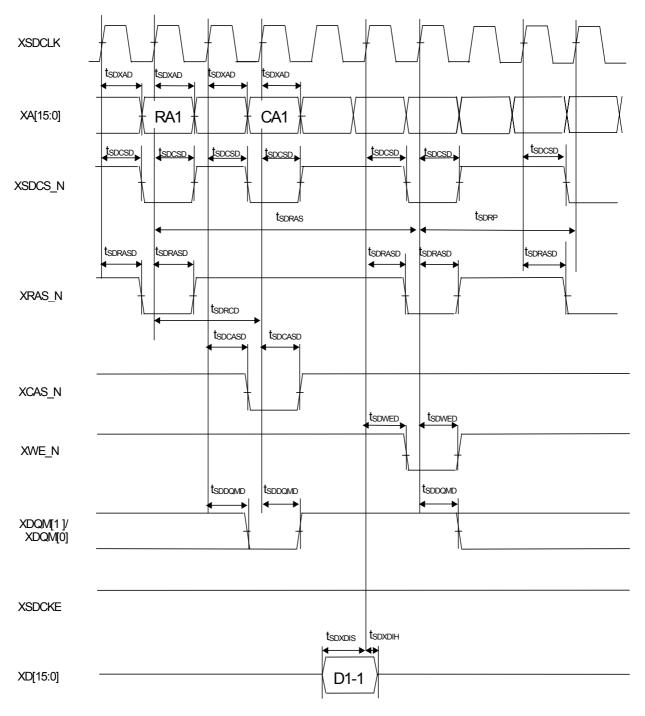

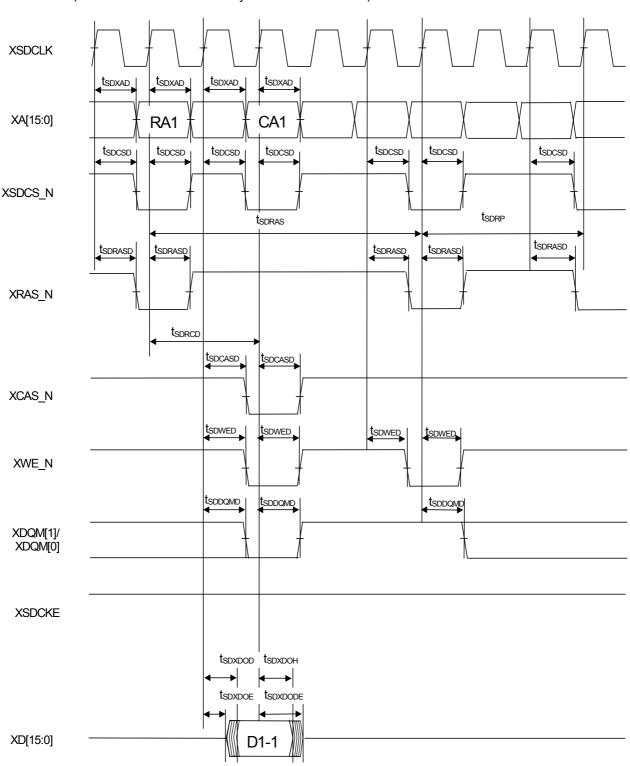

- Supports EDO DRAM and SDRAM

- Supports 16-bit and 8-bit (only possible for EDO DRAM) devices

- Supports distributed CAS before RAS (CBR) refresh

- External I/O banks access

- Four banks of external I/O space

- Supports 8- and 16-bit devices

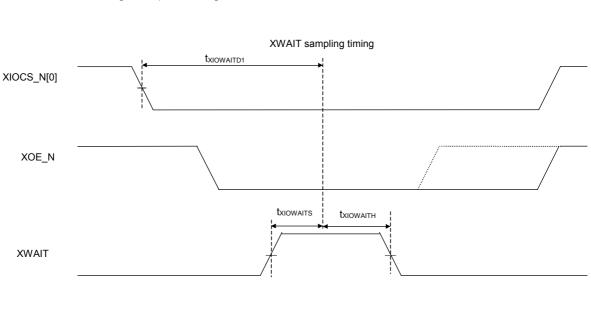

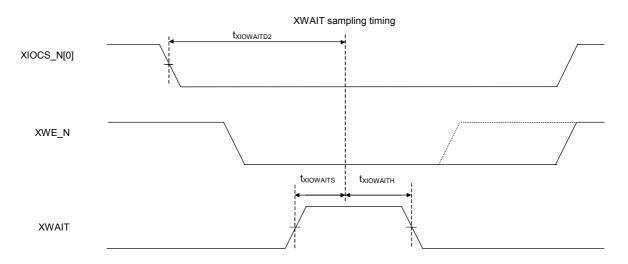

- Supports external WAIT input signal (XWAIT)

- SIO

- Full duplex asynchronous operation

- Built-in baud rate generator

- Synchronous SIO

- Choice of Master or Slave operation

- Choice of LSB or MSB fast operation

- I2C

- Master mode only

- Supports fast mode (400Kbps), standard mode (100Kbps)

- UART

- 16550A-compatible asynchronous communications

- 16-byte FIFO each for transmit and receive operations

- Full duplex collision operation

- Built-in baud rate generator

- Clock Signal

- Connects to crystal

- ML674001 series : 16 MHz to 33 MHz

- ML675001 series : 5MHz to 14 MHz

- Also supports direct external clock input

- Power Management

- STANDBY mode: Stop clock in software

- HALT mode: Stop clock signals to CPU and other key components in software

- Clock gear: clock change is dynamically possible in the division ratio of clock input frequency. ML674001 series : 1/1, 1/2, 1/4, 1/8, or 1/16

- ML675001 series : 1/1, 1/2, 1/4, 1/8, 1/16, or 1/32

- Functional blocks: Stop clock signals to individual function blocks

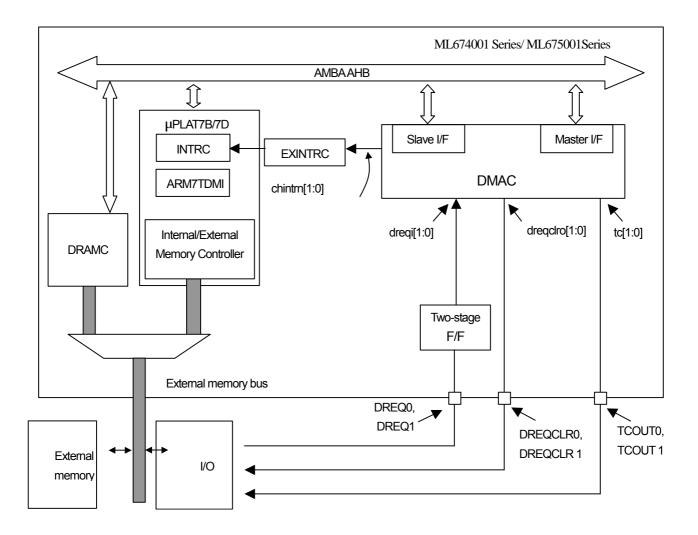

## 1.2 Functional Blocks

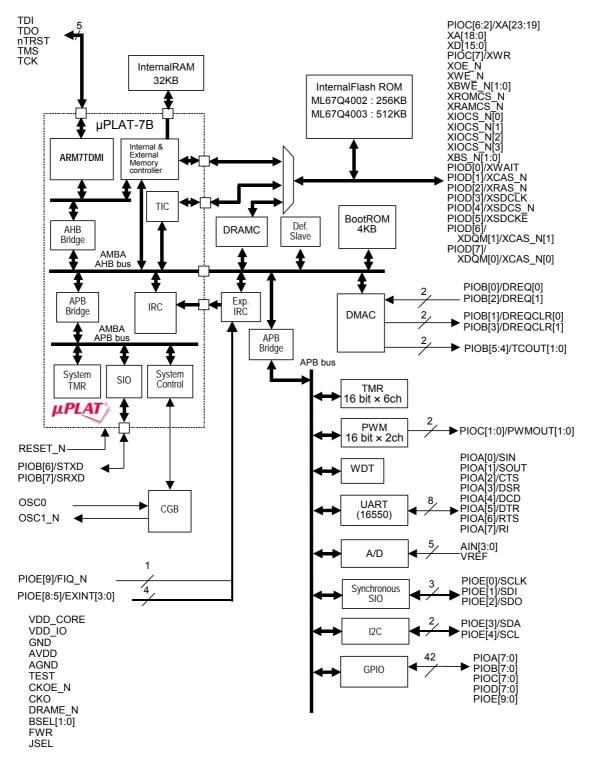

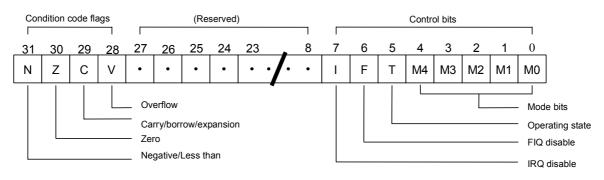

### 1.2.1 ML674001 series Block Diagram

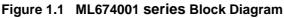

### 1.2.2 ML675001 series Block Diagram

## 1.3 Pins

### 1.3.1 Pin Layout

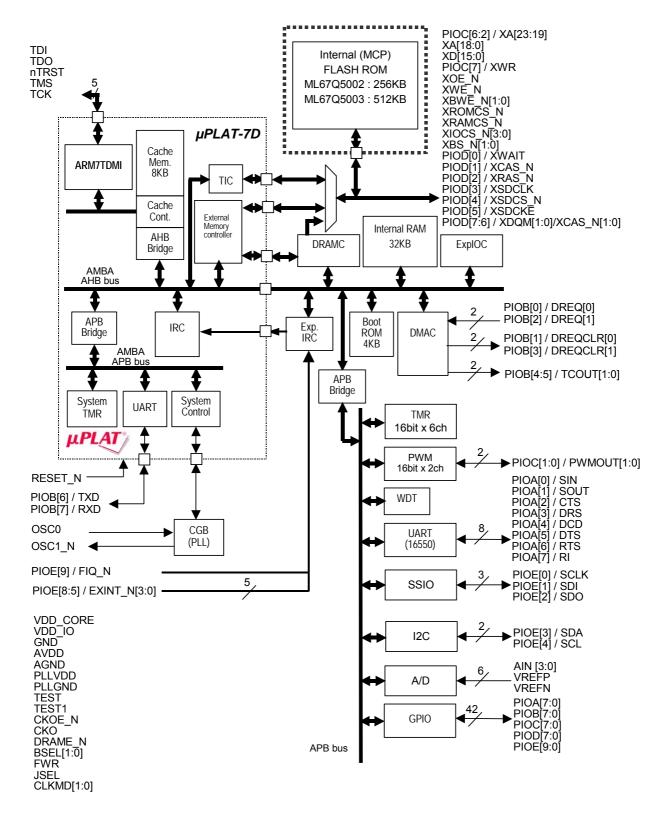

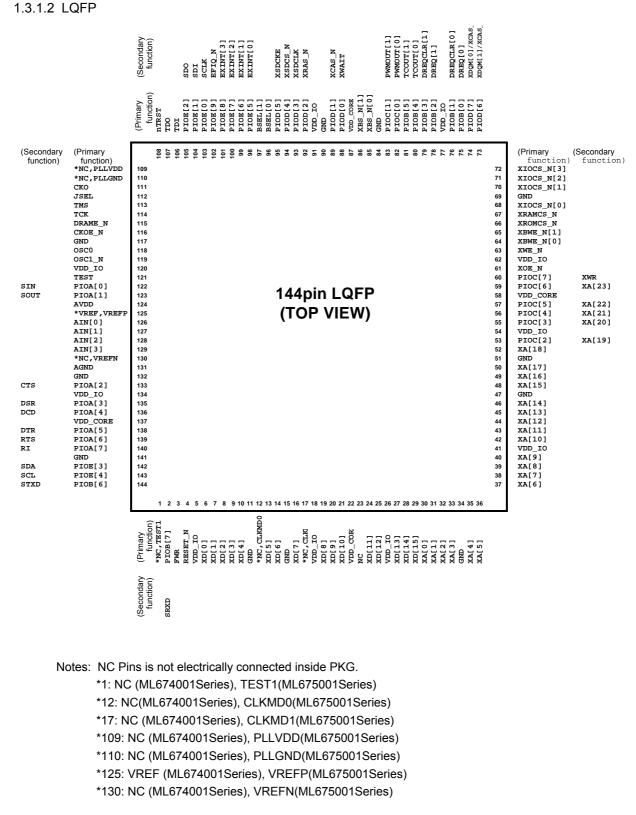

1.3.1.1 LFBGA

|   | 13                         | 12                       | 11                  | 10                        | 9               | 8                  | 7                   | 6                 | 5               | 4               | 3               | 2                  | 1                 |

|---|----------------------------|--------------------------|---------------------|---------------------------|-----------------|--------------------|---------------------|-------------------|-----------------|-----------------|-----------------|--------------------|-------------------|

| Ν | PIOD[6]/<br>XDQM[1<br>]    | XIOCS_<br>N[3]           | XIOCS_<br>N[1]      | XRAMC<br>S_N              | XBWE_<br>N[0]   | XOE_N              | PIOC[4]/<br>XA[21]  | XA[16]            | XA[14]          | XA[11]          | XA[9]           | XA[7]              | XA[6]             |

| м | PIOD[7]/<br>XDQM[0<br>]    | XIOCS_<br>N[2]           | XIOCS_<br>N[0]      | XWE_N                     | PIOC[7]/<br>XWR | PIOC[6]/<br>XA[23] | PIOC[2]/X<br>A[19]  | XA[17]            | XA[15]          | XA[13]          | XA[10]          | XA[4]              | XA[5]             |

| L | PIOB[1]/<br>DREQC<br>LR[0] | PIOB[2]/<br>DREQ[1]      | PIOB[0]/<br>DREQ[0] | XROMC<br>S_N              | XBWE_<br>N[1]   |                    |                     |                   |                 |                 |                 | XA[2]              | GND               |

| κ | PIOB[3]/<br>DREQC<br>LR[1] | PIOB[5]/<br>TCOUT[<br>1] | VDD_IO              | GND                       | VDD_IO          | VDD_C<br>ORE       | VDD_IO              | GND               | GND             | XA[3]           | XA[0]           | XD[13]             | XA[1]             |

| J | PIOC[0]/<br>PWMOU<br>T[0]  | GND                      |                     | PIOC[1]/<br>PWMOU<br>T[1] |                 |                    |                     |                   | VDD_IO          | XD[15]          | XD[11]          | XD[14]             |                   |

| н | XBS_N[<br>0]               | XBS_N[<br>1]             | PIOD[0]/<br>XWAIT   | VDD_C<br>ORE              |                 |                    |                     |                   |                 | VDD_C<br>ORE    | XD[10]          | NC                 | XD[12]            |

| G |                            | PIOD[1]/<br>XCAS_N       | VDD_IO              | GND                       |                 | •                  | oin LF<br>)P VIE    |                   |                 | VDD_IO          | XD[8]           | NC,<br>CLKMD1      | XD[9]             |

| F | BSEL[1]                    | PIOD[5]/<br>XSDCK<br>E   | PIOD[3]/<br>XSDCLK  | PIOD[4]/<br>XSDCS_<br>N   |                 |                    |                     | ŗ                 |                 | GND             | XD[7]           | XD[6]              | XD[5]             |

| Е | PIOE[7]/<br>EXINT[2]       | BSEL[0]                  |                     | PIOE[5]/<br>EXINT[0]      |                 |                    |                     |                   |                 | GND             | XD[2]           | NC,<br>CLKMD0<br>* | XD[4]             |

| D | PIOE[0]/<br>SCLK           | PIOE[6]/<br>EXINT[1]     |                     | PIOE[2]/<br>SDO           | OSC1_N          | PIOA[1]/<br>SOUT   | AIN[0]              | NC,<br>VREFN<br>* | GND             | VDD_IO          | XD[3]           | XD[1]              |                   |

| С | TDI                        | PIOE[1]/<br>SDI          | СКО                 | TMS                       | CKOE_<br>N      | AVDD               | AIN[1]              | AIN[3]            | PIOA[5]/<br>DTR | FWR             | XD[0]           | RESET_<br>N        |                   |

| в | nTRST                      | TDO                      | тск                 | GND                       | VDD_IO          | PIOA[0]/<br>SIN    | VREF,<br>VREFP<br>* | AGND              | GND             | PIOA[3]/<br>DSR | PIOA[7]/<br>RI  | PIOE[4]/<br>SCL    | PIOB[7]/<br>SRXD  |

| Α | NC,<br>PLLVDD<br>*         | NC,<br>PLLGND<br>*       | JSEL                | DRAME<br>_N               | OSC0            | TEST               | AIN[2]              | PIOA[2]/<br>CTS   | PIOA[4]/<br>DCD | PIOA[6]/<br>RTS | PIOE[3]/<br>SDA | PIOB[6]/<br>STXD   | NC,<br>TEST1<br>* |

| ' | 13                         | 12                       | 11                  | 10                        | 9               | 8                  | 7                   | 6                 | 5               | 4               | 3               | 2                  | 1                 |

Notes: NC Pins is not electrically connected inside PKG.

\*A1: NC (ML674001Series), TEST1(ML675001Series) \*E2: NC(ML674001Series), CLKMD0(ML675001Series) \*G2: NC (ML674001Series), CLKMD1(ML675001Series) \*A13: NC (ML674001Series), PLLVDD(ML675001Series) \*A12: NC (ML674001Series), PLLGND(ML675001Series) \*B7: VREF (ML674001Series), VREFP(ML675001Series) \*D6: NC (ML674001Series), VREFN(ML675001Series)

Figure 1.3 Pin Layout(LFGBA)

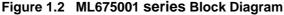

Figure 1.4 Pin Layout(LQFP)

### 1.3.2 Pin List

| Pin  |     |          | P   | rimary Function                        | S        | econd                                         | ary Function       |

|------|-----|----------|-----|----------------------------------------|----------|-----------------------------------------------|--------------------|

| LQFP | BGA | Symbol   | I/O | Description                            | Symbol   | I/O                                           | Description        |

| 1    | A1  | NC       | _   | NC (ML674001Series)                    | _        | _                                             |                    |

|      |     | TEST1    | I   | TEST Mode (ML675001Series)             | _        | —                                             |                    |

| 2    | B1  | PIOB[7]  | I/O | General port (with interrupt function) | SRXD     | I                                             | SIO receive signal |

| 3    | C3  | FWR      | I   | TEST Mode                              | _        | —                                             |                    |

| 4    | C1  | RESET_N  | I   | Reset input                            | —        | _                                             |                    |

| 5    | D3  | VDD_IO   | VDD | IO power supply                        | —        | -                                             |                    |

| 6    | C2  | XD[0]    | I/O | External data bus                      | —        | -                                             |                    |

| 7    | D1  | XD[1]    | I/O | External data bus                      | —        | —                                             |                    |

| 8    | E3  | XD[2]    | I/O | External data bus                      | —        | —                                             |                    |

| 9    | D2  | XD[3]    | I/O | External data bus                      | —        | —                                             |                    |

| 10   | E1  | XD[4]    | I/O | External data bus                      | —        | —                                             |                    |

| 11   | E4  | GND      | GND | GND                                    | —        | —                                             |                    |

| 12   | E2  | NC       | —   | NC (ML674001Series)                    | —        | —                                             |                    |

|      |     | CLKMD0   | I   | Clock mode input (ML675001Series)      | —        | —                                             |                    |

| 13   | F1  | XD[5]    | I/O | External data bus                      | —        | —                                             |                    |

| 14   | F2  | XD[6]    | I/O | External data bus                      | —        | —                                             |                    |

| 15   | F4  | GND      | GND | GND                                    | —        | —                                             |                    |

| 16   | F3  | XD[7]    | I/O | External data bus                      | —        | —                                             |                    |

| 17   | G2  | NC       | —   | NC (ML674001Series)                    | —        | —                                             |                    |

|      |     | CLKMD1   | Ι   | Clock mode input (ML675001Series)      | —        | —                                             |                    |

| 18   | G4  | VDD_IO   | VDD | I/O power supply                       | —        | —                                             |                    |

| 19   | G3  | XD[8]    | I/O | External data bus                      | _        | —                                             |                    |

| 20   | G1  | XD[9]    | I/O | External data bus                      | —        | —                                             |                    |

| 21   | H3  | XD[10]   | I/O | External data bus                      | —        | —                                             |                    |

| 22   | H4  | VDD_CORE | VDD | CORE power supply                      | —        | —                                             |                    |

| 23   | H2  | NC       | _   | NC                                     | —        | —                                             |                    |

| 24   | J2  | XD[11]   | I/O | External data bus                      | —        | —                                             |                    |

| 25   | H1  | XD[12]   | I/O | External data bus                      | _        | —                                             |                    |

| 26   | J4  | VDD_IO   | VDD | I/O power supply                       | —        | —                                             |                    |

| 27   | K2  | XD[13]   | I/O | External data bus                      | —        | —                                             |                    |

| 28   | J1  | XD[14]   | I/O | External data bus                      | —        | —                                             |                    |

| 29   | J3  | XD[15]   | I/O | External data bus                      | —        | —                                             |                    |

| 30   | K3  | XA[0]    | 0   | External address output                | —        | <u> </u>                                      |                    |

| 31   | K1  | XA[1]    | 0   | External address output                | —        | —                                             |                    |

| 32   | L2  | XA[2]    | 0   | External address output                | —        | <u> </u>                                      |                    |

| 33   | K4  | XA[3]    | 0   | External address output                | —        | <u> </u>                                      |                    |

| 34   | L1  | GND      | GND | GND                                    | —        | <u> </u>                                      |                    |

| 35   | M2  | XA[4]    | 0   | External address output                | <u> </u> | <u>                                      </u> |                    |

| 36   | M1  | XA[5]    | 0   | External address output                | _        | —                                             |                    |

| 37   | N1  | XA[6]    | 0   | External address output                | —        | <u> </u>                                      |                    |

| 38   | N2  | XA[7]    | 0   | External address output                | —        | <u> </u>                                      |                    |

| 39   | L3  | XA[8]    | 0   | External address output                | —        | <u> </u>                                      |                    |

| 40   | N3  | XA[9]    | 0   | External address output                | —        | —                                             |                    |

## ML674001 Series/ML675001 Series User's Manual Chapter 1 Introduction

| Pin  |     |              | P   | imary Function                         | Se                    | econd | ary Function                   |

|------|-----|--------------|-----|----------------------------------------|-----------------------|-------|--------------------------------|

| LQFP | BGA | Symbol       | I/O | Description                            | Symbol                | I/O   | Description                    |

| 41   | L4  | VDD_IO       | VDD | I/O power supply                       | _                     | _     | · ·                            |

| 42   | M3  | <br>XA[10]   | 0   | External address output                | _                     | _     |                                |

| 43   | N4  | XA[11]       | 0   | External address output                | _                     | _     |                                |

| 44   | L5  | XA[12]       | 0   | External address output                | _                     | _     |                                |

| 45   | M4  | XA[13]       | 0   | External address output                | _                     | _     |                                |

| 46   | N5  | XA[14]       | 0   | External address output                | _                     | - 1   |                                |

| 47   | K5  | GND          | GND | GND                                    | _                     | _     |                                |

| 48   | M5  | XA[15]       | 0   | External address output                | _                     | _     |                                |

| 49   | N6  | XA[16]       | 0   | External address output                | _                     | _     |                                |

| 50   | M6  | XA[17]       | 0   | External address output                | _                     | _     |                                |

| 51   | K6  | GND          | GND | GND                                    | _                     | _     |                                |

| 52   | L6  | XA[18]       | 0   | External address output                | _                     | _     |                                |

| 53   | M7  | PIOC[2]      | I/O | General port (with interrupt function) | XA[19]                | 0     | External address output        |

| 54   | K7  | VDD_IO       | VDD | I/O power supply                       | _                     | _     |                                |

| 55   | L7  | PIOC[3]      | I/O | General port (with interrupt function) | XA[20]                | 0     | External address output        |

| 56   | N7  | PIOC[4]      | I/O | General port (with interrupt function) | XA[21]                | 0     | External address output        |

| 57   | L8  | PIOC[5]      | I/O | General port (with interrupt function) | XA[22]                | 0     | External address output        |

| 58   | K8  | VDD_CORE     | VDD | CORE power supply                      | _                     | _     |                                |

| 59   | M8  | –<br>PIOC[6] | I/O | General port (with interrupt function) | XA[23]                | 0     | External address output        |

| 60   | M9  | PIOC[7]      | I/O | General port (with interrupt function) | XWR                   | 0     | Transfer direction of          |

|      | -   |              |     |                                        |                       |       | external bus                   |

| 61   | N8  | XOE_N        | 0   | Output enable (excluding SDRAM)        | _                     | —     |                                |

| 62   | K9  | VDD_IO       | VDD | I/O power supply                       | —                     | —     |                                |

| 63   | M10 | XWE_N        | 0   | Write enable                           | —                     | —     |                                |

| 64   | N9  | XBWE_N[0]    | 0   | Byte write enable (LSB)                | —                     | —     |                                |

| 65   | L9  | XBWE_N[1]    | 0   | Byte write enable (MSB)                | —                     | —     |                                |

| 66   | L10 | XROMCS_N     | 0   | External ROM chip select               | —                     | —     |                                |

| 67   | N10 | XRAMCS_N     | 0   | External RAM chip select               | —                     | —     |                                |

| 68   | M11 | XIOCS_N[0]   | 0   | IO chip select 0                       | —                     | —     |                                |

| 69   | K10 | GND          | GND | GND                                    | —                     | —     |                                |

| 70   | N11 | XIOCS_N[1]   | 0   | IO chip select 1                       | —                     | —     |                                |

| 71   | M12 | XIOCS_N[2]   | 0   | IO chip select 2                       | —                     | —     |                                |

| 72   | N12 | XIOCS_N[3]   | 0   | IO chip select 3                       | —                     | —     |                                |

| 73   | N13 | PIOD[6]      | I/O | General port (with interrupt function) | XDQM[1]/XCA<br>S_N[1] | 0     | INPUT/OUTPUT<br>mask/CAS (MSB) |

| 74   | M13 | PIOD[7]      | I/O | General port (with interrupt function) | XDQM[0]/XCA<br>S_N[0] | 0     | INPUT/OUTPUT<br>mask/CAS (LSB) |

| 75   | L11 | PIOB[0]      | I/O | General port (with interrupt function) | DREQ[0]               | I     | DMA request signal (CH0)       |

| 76   | L13 | PIOB[1]      | I/O | General port (with interrupt function) | DREQCLR[0]            | 0     | DREQ Clear Signal (CH0)        |

| 77   | K11 | VDD_IO       | VDD | I/O power supply                       | <b> </b> _            | _     |                                |

| 78   | L12 | PIOB[2]      | I/O | General port (with interrupt function) | DREQ[1]               | I     | DMA request signal (CH1)       |

| 79   | K13 | PIOB[3]      | I/O | General port (with interrupt function) | DREQCLR[1]            | 0     | DREQ Clear Signal (CH1)        |

| 80   | J11 | PIOB[4]      | I/O | General port (with interrupt function) | TCOUT[0]              | 0     | DMAC Terminal Count<br>(CH0)   |

| 81   | K12 | PIOB[5]      | I/O | General port (with interrupt function) | TCOUT[1]              | 0     | DMAC Terminal Count            |

# ML674001 Series/ML675001 Series User's Manual Chapter 1 Introduction

| Pin             |     |          | Pi          | rimary Function                        | Secondary Function |             |                                           |  |

|-----------------|-----|----------|-------------|----------------------------------------|--------------------|-------------|-------------------------------------------|--|

| LQFP BGA Symbol |     | I/O      | Description | Symbol                                 | I/O                | Description |                                           |  |

|                 |     |          |             |                                        |                    |             | (CH1)                                     |  |

| 82              | J13 | PIOC[0]  | I/O         | General port (with interrupt function) | PWMOUT[0]          | 0           | PWM output (CH0)                          |  |

| 83              | J10 | PIOC[1]  | I/O         | General port (with interrupt function) | PWMOUT[1]          | 0           | PWM output (CH1)                          |  |

| 84              | J12 | GND      | GND         | GND                                    | _                  | _           |                                           |  |

| 85              | H13 | XBS_N[0] | 0           | External bus byte select (LSB)         | _                  | _           |                                           |  |

| 86              | H12 | XBS_N[1] | 0           | External bus byte select (MSB)         | _                  | _           |                                           |  |

| 87              | H10 | VDD_CORE | VDD         | CORE power supply                      | _                  | _           |                                           |  |

| 88              | H11 | PIOD[0]  | I/O         | General port (with interrupt function) | XWAIT              | I           | Wait input signal for I/O<br>Bank 0/1/2/3 |  |

| 89              | G12 | PIOD[1]  | I/O         | General port (with interrupt function) | XCAS_N             | 0           | Column address strobe<br>(SDRAM)          |  |

| 90              | G10 | GND      | GND         | GND                                    | —                  | _           |                                           |  |

| 91              | G11 | VDD_IO   | VDD         | I/O power supply                       | —                  | _           |                                           |  |

| 92              | G13 | PIOD[2]  | I/O         | General port (with interrupt function) | XRAS_N             | 0           | Row address strobe<br>(SDRAM/EDO-DRAM)    |  |

| 93              | F11 | PIOD[3]  | I/O         | General port (with interrupt function) | XSDCLK             | 0           | Clock for SDRAM                           |  |

| 94              | F10 | PIOD[4]  | I/O         | General port (with interrupt function) | XSDCS_N            | 0           | Chip select for SDRAM                     |  |

| 95              | F12 | PIOD[5]  | I/O         | General port (with interrupt function) | XSDCKE             | 0           | Clock enable (SDRAM)                      |  |

| 96              | E12 | BSEL[0]  | I           | Select boot device                     | —                  | —           |                                           |  |

| 97              | F13 | BSEL[1]  | Ι           | Select boot device                     | —                  | _           |                                           |  |

| 98              | E10 | PIOE[5]  | I/O         | General port (with interrupt function) | EXINT[0]           | Ι           | Interrupt input                           |  |

| 99              | D12 | PIOE[6]  | I/O         | General port (with interrupt function) | EXINT[1]           | Ι           | Interrupt input                           |  |

| 100             | E13 | PIOE[7]  | I/O         | General port (with interrupt function) | EXINT[2]           | Ι           | Interrupt input                           |  |

| 101             | E11 | PIOE[8]  | I/O         | General port (with interrupt function) | EXINT[3]           | Ι           | Interrupt input                           |  |

| 102             | D11 | PIOE[9]  | I/O         | General port (with interrupt function) | EFIQ_N             | Ι           | FIQ input                                 |  |

| 103             | D13 | PIOE[0]  | I/O         | General port (with interrupt function) | SCLK               | I/O         | SSIO clock                                |  |

| 104             | C12 | PIOE[1]  | I/O         | General port (with interrupt function) | SDI                | Ι           | SSIO Serial Data In                       |  |

| 105             | D10 | PIOE[2]  | I/O         | General port (with interrupt function) | SDO                | 0           | SSIO Serial Data Out                      |  |

| 106             | C13 | TDI      | Ι           | JTAG Data Input                        | _                  | _           |                                           |  |

| 107             | B12 | TDO      | 0           | JTAG data out                          | _                  | _           |                                           |  |

| 108             | B13 | nTRST    | I           | JTAG reset                             | _                  | —           |                                           |  |

| 109             | A13 | NC       | —           | NC (ML674001Series)                    | _                  | —           |                                           |  |

|                 |     | PLLVDD   | VDD         | PLL power supply (ML675001Series)      | _                  | —           |                                           |  |

| 110             | A12 | NC       | —           | NC (ML674001Series)                    | _                  | —           |                                           |  |

|                 |     | PLLGND   | GND         | PLL GND (ML675001Series)               | _                  | —           |                                           |  |

| 111             | C11 | СКО      | 0           | Clock output                           | _                  | _           |                                           |  |

| 112             | A11 | JSEL     | I           | JTAG select                            | —                  | _           |                                           |  |

| 113             | C10 | TMS      | I           | JTAG mode select                       | —                  |             |                                           |  |

| 114             | B11 | тск      | I           | JTAG clock                             | —                  |             |                                           |  |

| 115             | A10 | DRAME_N  | I           | DRAM enable                            | —                  |             |                                           |  |

| 116             | C9  | CKOE_N   | I           | Clock out enable                       | —                  | —           |                                           |  |

| 117             | B10 | GND      | GND         | GND                                    | —                  |             |                                           |  |

| 118             | A9  | OSC0     | I           | Oscillation input pin                  | —                  |             |                                           |  |

| 119             | D9  | OSC1_N   | 0           | Oscillation output pin                 | —                  |             |                                           |  |

| 120             | B9  | VDD_IO   | VDD         | IO power supply                        | —                  | —           |                                           |  |

| Pi   | in  |          | Pi       | rimary Function                        | S      | econd | ary Function                |

|------|-----|----------|----------|----------------------------------------|--------|-------|-----------------------------|

| LQFP | BGA | Symbol   | I/O      | Description                            | Symbol | I/O   | Description                 |

| 121  | A8  | TEST     | Ι        | Test mode input                        | —      | _     |                             |

| 122  | B8  | PIOA[0]  | I/O      | General port (with interrupt function) | SIN    | Ι     | UART Serial Data In         |

| 123  | D8  | PIOA[1]  | I/O      | General port (with interrupt function) | SOUT   | 0     | UART Serial Data Out        |

| 124  | C8  | AVDD     | VDD      | A/D CONVERTER power supply             | —      | _     |                             |

| 125  | B7  | VREF     | I        | A/D CONVERTER Reference voltage        | —      | _     |                             |

|      |     |          |          | (ML674001Series)                       |        |       |                             |

|      |     | VREFP    | I        | A/D CONVERTER Reference voltage        | —      | —     |                             |

|      |     |          |          | (ML675001Series)                       |        |       |                             |

| 126  | D7  | AIN[0]   | I.       | A/D CONVERTER                          | —      | —     |                             |

|      |     |          |          | analog input port                      |        |       |                             |

| 127  | C7  | AIN[1]   | I        | A/D CONVERTER                          | —      | -     |                             |

|      |     |          | <u> </u> | analog input port                      |        |       |                             |

| 128  | A7  | AIN[2]   | I        | A/D CONVERTER<br>analog input port     | —      | -     |                             |

| 129  | C6  | AIN[3]   | 1        | A/D CONVERTER                          |        |       |                             |

| 129  | 00  | Anijoj   | 1        | analog input port                      | _      | _     |                             |

| 130  | D6  | NC       | _        | NC (ML674001Series)                    | _      | -     |                             |

|      |     | VREFN    | GND      | A/D CONVERTER Reference GND            |        |       |                             |

|      |     |          |          | (ML675001Series)                       |        |       |                             |

| 131  | B6  | AGND     | GND      | GND for A/D CONVERTER                  | _      | _     |                             |

| 132  | B5  | GND      | GND      | GND                                    | —      | —     |                             |

| 133  | A6  | PIOA[2]  | I/O      | General port (with interrupt function) | CTS    | I     | UART Clear To Send          |

| 134  | D5  | VDD_IO   | VDD      | IO power supply                        | —      | -     |                             |

| 135  | B4  | PIOA[3]  | I/O      | General port (with interrupt function) | DSR    | Ι     | UART Set Ready              |

| 136  | A5  | PIOA[4]  | I/O      | General port (with interrupt function) | DCD    | Ι     | UART Carrier Detect         |

| 137  | C5  | VDD_CORE | VDD      | CORE power supply                      | —      | —     |                             |

| 138  | C4  | PIOA[5]  | I/O      | General port (with interrupt function) | DTR    | 0     | UART Data Terminal<br>Ready |

| 139  | A4  | PIOA[6]  | I/O      | General port (with interrupt function) | RTS    | 0     | UART Request To Send        |

| 140  | B3  | PIOA[7]  | I/O      | General port (with interrupt function) | RI     | I     | UART Ring Indicator         |

| 141  | D4  | GND      | GND      | GND                                    | _      | _     |                             |

| 142  | A3  | PIOE[3]  | I/O      | General port (with interrupt function) | SDA    | I/O   | I2C Data In/Out             |

| 143  | B2  | PIOE[4]  | I/O      | General port (with interrupt function) | SCL    | 0     | I2C Clock out               |

| 144  | A2  | PIOB[6]  | I/O      | General port (with interrupt function) | STXD   | 0     | SIO send data output        |

## 1.3.3 Pin Descriptions

| Pin Name          | I/O      | Description                                                                     | Primary/  | Logic    |

|-------------------|----------|---------------------------------------------------------------------------------|-----------|----------|

|                   |          |                                                                                 | Secondary | 9        |

| System            | _        |                                                                                 |           |          |

| RESET_N           | Ι        | Reset input                                                                     | —         | Negative |

| BSEL[1:0]         | Ι        | Boot device select signal                                                       |           | Positive |

|                   |          | BSEL[1] BSEL[0] Boot device                                                     |           |          |

|                   |          | 0 0 Internal Flash                                                              |           |          |

|                   |          | 0 1 External ROM                                                                | —         |          |

|                   |          | 1 * Boot mode                                                                   |           |          |

|                   |          | The selected device is mapped to BANK0 (0x0000_0000 - 0x07 FF_FFF) after reset. |           |          |

| CLKMD[1:0]        | I        | Clock mode input.                                                               | _         | Positive |

| OSC0              | I        | Crystal connection or external clock input.                                     |           |          |

|                   |          | Connect a crystal , if used, to OSC0 and OSC1_N.                                |           |          |

|                   |          | (ML674001Series:16 MHz to 33 MHz)                                               |           |          |

|                   |          | (ML675001Series:5 MHz to 14 MHz)                                                | _         | _        |

|                   |          | It is also possible to input a direct clock.                                    |           |          |

|                   |          | (ML674001Series:1 MHz to 33 MHz)                                                |           |          |

|                   |          | (ML675001Series:5 MHz to 14 MHz, 20MHz to 56MHz)                                |           |          |

| OSC1_N            | 0        | Oscillation output pin                                                          |           |          |

|                   |          | When not using a crystal, leave this pin unconnected.                           | _         | _        |

| СКО               | 0        | Clock out                                                                       | —         | _        |

| CKOE_N            | Ι        | Clock out enable                                                                | _         | Negative |

| Debugging suppor  | t.       |                                                                                 |           |          |

| тск               | I        | Debugging pin. Normally connect to ground level.                                | _         | _        |

| TMS               | I        | Debugging pin. Normally drive at High level.                                    | _         | Positive |

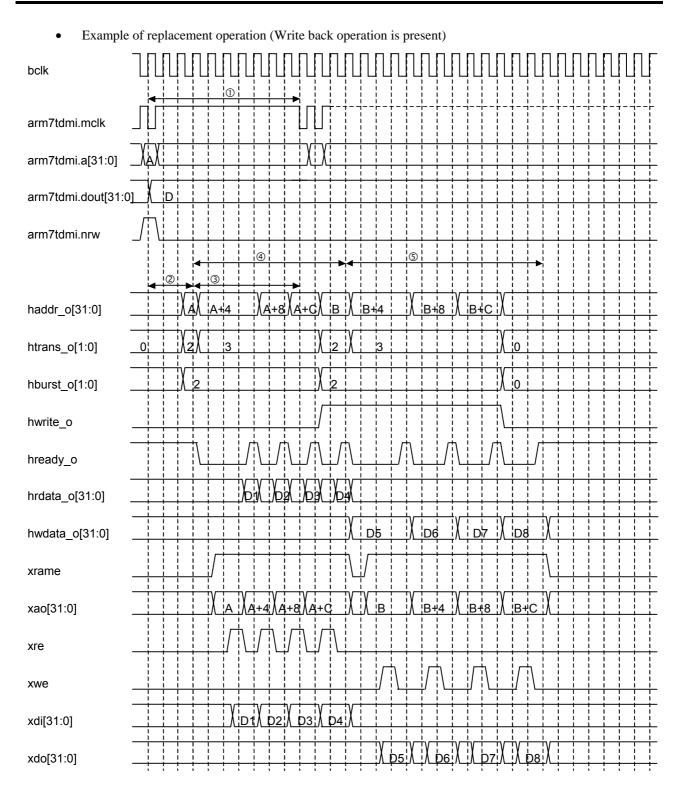

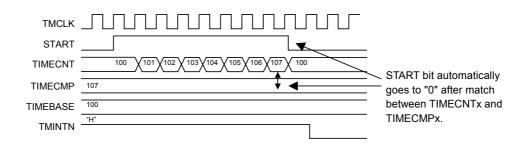

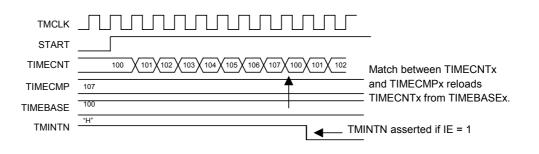

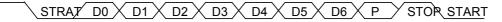

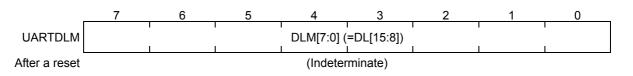

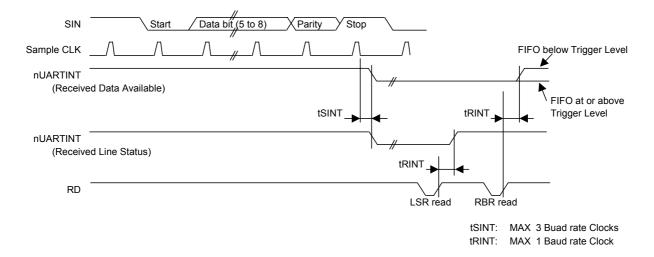

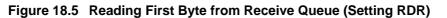

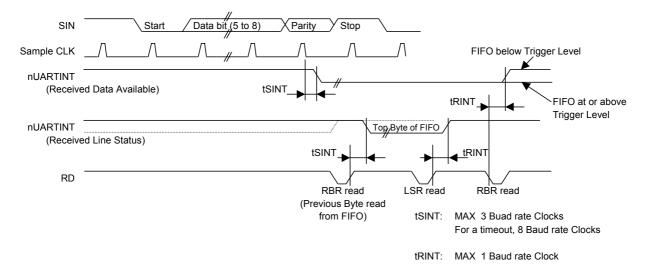

| nTRST             | 1        | Debugging pin. Normally connect to ground level.                                | _         | Negative |